FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Timing Analysis of Real-Time Systems Considering the Contention on the Shared Interconnection Network in Multicores

Dakshina Dasari

Doctoral Programme in Electrical and Computer Engineering

Supervisor: Dr. Vincent Nélis

May 14, 2014

$\bigodot$ Dakshina Dasari, 2014

# Timing Analysis of Real-Time Systems Considering the Contention on the Shared Interconnection Network in Multicores

Dakshina Dasari

Doctoral Programme in Electrical and Computer Engineering

# Abstract

Multicore technology has been heralded as one of the course-changing computing technologies, providing new levels of energy-efficient performance, enabled by advanced parallel processing and miniaturization techniques. This is evident by the fact that every leading chip designer has a multicore processor as a part of its product offerings and also by witnessing the proliferation of this technology across the entire range of embedded devices. Real-time embedded systems are no exception to this trend either. By definition, a key requirement for real-time embedded systems is to be able to deliver their functional behaviour within specific time bounds. However, while the computational capabilities of multicores are indisputable, they must be assessed for their predictability before employing them to host real-time applications which have strict timing requirements. While the study of timing analysis for uniprocessors is in its mature stages, given the decades of research dedicated to it, the timing analysis in the domain of multicores is still in its nascent stages.

The broader focus of this thesis is to address the timing analysis challenge in multicores: specifically on determining the impact of shared resources like the shared bus (or NoC's in many-core systems) on the execution time of the real-time tasks, when deployed on these multicores. To elaborate, in typical implementation of multicore systems, multiple cores access the main memory via a shared channel (like the front side bus). This often leads to contention on this shared channel, which results in an increase of the execution time and the response time of the tasks. Computing the upper bounds on these timing parameters is a vital prerequisite for the deployment of real-time tasks on these multicores and is an relatively new area of research. The work in this thesis aims at meeting this objective of providing and validating methods for the timing analysis of applications executed on multicore and many-core platforms which inherently do not guarantee predictability.

The main contributions include proposing a model to derive the memory profile of tasks and the memory request profile of a core for a given time interval. This is extended further to propose a general framework to model the availability of the shared bus, using the memory profile of the analyzed task in finer granularity and to be able to deal with different bus arbitration mechanisms. This work has also been extended to the realm of the "Many-Core" systems, by proposing a method to derive the worst-case traversal time for a mesh-based interconnect network. The thesis also delves into memory controller analysis and as an interesting case study provides temporal analysis of Phase change memory based multicore systems, which unlike DRAM based systems, have noticeably different read and write latencies.

# Resumo

As tecnologias baseadas em sistemas multi-processador estão a mudar os sistemas computacionais, proporcionando novos níveis de desempenho na eficiência energética, devido à utilização de técnicas avançadas de processamento paralelo e miniaturização dos componentes. Isto é evidenciado pelo facto de todos os principais construtores de processadores terem nas suas linhas de produtos, processadores baseados na arquitectura multi-processador. Também se tem verificado uma massificação da utilização deste tipo de processadores em sistemas embebidos, em geral, e, mais especificamente, também nos sistemas embebidos utilizados em sistemas de tempo real. Por definição, um sistema de tempo real deve produzir correctamente os resultados dentro de um limite temporal, isto é, os resultados só são válidos se forem disponibilizados dentro intervalos de tempo bem definidos. Apesar de os sistemas multi-processador não suscitarem muitas dúvidas em relação à sua capacidade de processamento, estes devem ser estudados e avaliados por forma a garantir que as restrições temporais (apresentadas pelos sistemas de tempo real) são garantidas. Enguanto que o estudo da analise temporal para sistemas uni-processador está num estado considerado maduro, fruto da várias décadas de investigação dedicadas a este tipo de sistemas, a análise temporal para sistemas multi-processador está ainda num estado inicial.

Em sentido lato, nesta dissertação são endereçados os desafios associados à análise temporal para sistemas multi-processador. Em detalhe, é determinado o impacto dos recursos partilhados, como por exemplo o barramento de acesso à memória partilhado pelos vários processadores, no tempo de execução das tarefas (constituintes do sistema de tempo real). Tipicamente, num sistema multi-processador, os vários processadores acedem à memória principal através de um único canal (ou barramento), logo é partilhado por todos. A utilização deste canal é exclusiva, o que implica que estes processadores disputam-no sempre que pretendem aceder à memória principal. Ora, isto tem impacto quer no tempo de execução quer no tempo de resposta das tarefas. Determinar os limites temporais máximos associados, por exemplo, à utilização do canal de acesso à memória é um pré-requisito vital para assegurar que as restrições temporais das tarefas são garantidas. E desta forma assegurar o correcto desempenho de um sistema de tempo real numa arquitectura multiprocessador. O trabalho apresentado nesta dissertação tem como objectivo definir e validar métodos de análise temporal para aplicações de tempo real a executar em arquitecturas multi-processador. Para tal foi criado um sistema genérico que permite modelar a disponibilidade do canal partilhado (com baseperfis de memória das tarefas) independente da política usada no acesso ao canal partilhado.

As principais contribuições incluem a proposta de um modelo para derivar perfis de uso da memória por parte das tarefas e perfis dos pedidos de acesso à memória por parte dos processadores num determinado intervalo temporal. Com a informação obtida por esse modelos é possível efectuar uma análise baseada no tempo de resposta das tarefas. Este trabalho foi também estendido para suportar sistemas multi-processador cuja interligação entre os processadores e a memória é baseada numa rede com uma configuração em malha. No decorrer do trabalho desenvolvido no contexto desta dissertação foi efectuada uma analise de controladores de memória e como caso de estudo é apresentada uma análise temporal para sistemas baseados PCM (*Phase-Change Memory*) em arquitecturas multi-processador, que contrariamente aos sistemas baseados em DRAM (*Dynamic Random Access Memory*), tem diferentes latências nas operações de leitura e escrita.

# Acknowledgments

Feeling gratitude and not expressing it is like wrapping a present and not giving it.

William Arthur Ward

Reaching this milestone would have not been possible without the support of many people. An exceptional friend and advisor, Vincent Nélis to whom I offer my heartfelt gratitude for his excellent guidance, patience, constructive reviews and for unconditionally standing by me throughout this journey. I would like to thank Eduardo Tovar who went the extra mile to ensure a conducive research environment and was always approachable. I have had the privilege of collaborating with Arvind Easwaran, Bjorn Andersson, Stefan M. Petters, Borislav Nikolic, Daniel Mosse and Benny Akesson along with Vincent at different phases of my research. I will forever treasure the interactions with them; their energy, technical acumen and enthusiasm was contagious and the teamwork saw us through various obstacles.

I would like to acknowledge Paulo Baltarejo Sousa for translating the abstract of the thesis in Portuguese. Thanks to the administration and the technical staff at CISTER for handling all the related glitches and providing a smooth work environment.

I feel lucky to be sharing my workspace with Boris, Artem, Ali, Kos, Guru and Jose, who were competitive, worked hard and partied harder – with these people around, it was always great to be at the lab. The drabness and monotony in life were superseded by the increased fun quotient during this phase, thanks to colleagues and friends, especially Patrick, Geoffrey, Vikram, Ali, Shashank, Ganga, Sujit, Anuj, Kiran and Kritika – I will always cherish the delicious dinners and board-game evenings!

My family has been extremely supportive of my work and I could not be here without them. Finally, these acknowledgements would be incomplete without whole heartedly thanking Guru, my husband, colleague, my best friend. Life has been a joyful rollercoaster ride with you around. Thanks for the wonderful dinners you made whenever I had deadlines and arrived late. Thanks for just being there for me and with me, whenever I needed you.

This work was partially supported by FCT (Fundação para a Ciência e Tecnologia) under the individual doctoral grant SFRH / BD / 71169 / 2010. vi

# List of Author's Publications

This is a list of papers and publications that reflects the results achieved during the development of the research work presented in this dissertation. A significant part of this thesis is compiled from these papers and publications.

### Journals

• Dakshina Dasari, Borislav Nikolic, Vincent Nélis and Stefan M. Petters, "NoC Contention Analysis using a Branch and Prune Algorithm", *ACM Transaction on Embedded Computing* (Accepted for publication).

### Conferences

- Dakshina Dasari, Vincent Nélis and Daniel Mosse, "Timing analysis of PCM Main Memory in Multicore Systems", In Proceedings of the 19th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA 2013).

- Dakshina Dasari, Benny Åkesson, Vincent Nélis, Muhammad Ali Awan, Stefan M. Petters, "Identifying the Sources of Unpredictability in COTS-based Multicore Systems", In Proceedings of the 8th IEEE International Symposium on Industrial Embedded Systems (SIES 2013),

- Dakshina Dasari and Vincent Nélis, "An Analysis of the Impact of Bus Contention on the WCET in Multicores", In Proceedings of the 9th IEEE International Conference on Embedded Software and Systems (ICESS-2012),

- Dakshina Dasari, Björn Andersson, Vincent Nélis, Stefan M. Petters, Arvind Easwaran and Jinkyu Lee, "Response Time Analysis of COTS-Based Multicores Considering The Contention On The Shared Memory Bus", In Proceedings of the 8th IEEE International Conference on Embedded Software and Systems (IEEE ICESS-11),

## **Under Submission**

• Dakshina Dasari, Vincent Nélis, and Benny Akesson, "Unified Framework for Bus Contention Analysis in Multicores" viii

# Contents

| 1        | Intr                                                           | oduction                                                                  | 1   |  |  |

|----------|----------------------------------------------------------------|---------------------------------------------------------------------------|-----|--|--|

|          | 1.1                                                            | Introduction to Embedded systems                                          | 1   |  |  |

|          | 1.2                                                            | Real-Time Embedded Systems                                                | 3   |  |  |

|          | 1.3                                                            | Paradigm shifts in the design of embedded systems                         | 9   |  |  |

|          | 1.4                                                            | Computing Platforms                                                       | 11  |  |  |

|          | 1.5                                                            | Overview of a typical many core system                                    | 16  |  |  |

|          | 1.6                                                            | Problems addressed in this thesis                                         | 19  |  |  |

|          | 1.7                                                            | Motivation and Relevance of this work                                     | 22  |  |  |

|          | 1.8                                                            | Thesis Organization                                                       | 28  |  |  |

| <b>2</b> | Background and Related work 31                                 |                                                                           |     |  |  |

|          | 2.1                                                            | Timing Analysis                                                           | 31  |  |  |

|          | 2.2                                                            | Timing Analysis: Uniprocessors to Multicore systems                       | 34  |  |  |

|          | 2.3                                                            | Related Work                                                              | 48  |  |  |

|          | 2.4                                                            | Scope for further work                                                    | 53  |  |  |

| 3        | Con                                                            | nputing Per-Task and Per-Core Memory Request Profiles                     | 57  |  |  |

|          | 3.1                                                            | Introduction                                                              | 57  |  |  |

|          | 3.2                                                            | System and Task Model                                                     | 61  |  |  |

|          | 3.3                                                            | Per-Task Cache Analysis                                                   | 62  |  |  |

|          | 3.4                                                            | Per-Task Memory Profile Analysis                                          | 64  |  |  |

|          | 3.5                                                            | Per-Core Memory Profile Analysis                                          | 69  |  |  |

|          | 3.6                                                            | Computation of the Per-Core Request Profile                               | 73  |  |  |

|          | 3.7                                                            | Correctness and properties of the $PCRP_p(t)$ function                    | 78  |  |  |

|          | 3.8                                                            | Optimization and Computational Complexity                                 | 81  |  |  |

|          | 3.9                                                            | Adaptations of PCRP() and Integration with existing work                  | 83  |  |  |

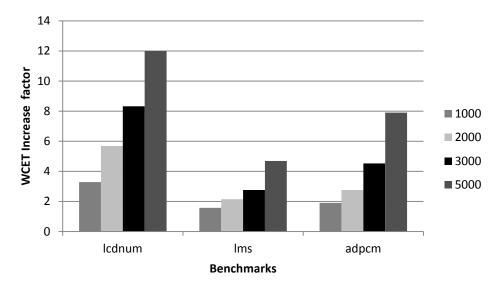

|          | 3.10                                                           | PCRP case study: WCET analysis                                            | 86  |  |  |

|          |                                                                | System wide Analysis                                                      | 88  |  |  |

|          |                                                                | Performance Comparison: Simulations                                       | 89  |  |  |

|          |                                                                | A method to obtain the parameters experimentally                          | 94  |  |  |

|          |                                                                | Chapter Summary                                                           | 97  |  |  |

| 4        | Unified Framework for Bus Contention Analysis in Multicores 99 |                                                                           |     |  |  |

|          | 4.1                                                            | System and Task Modeling                                                  | 100 |  |  |

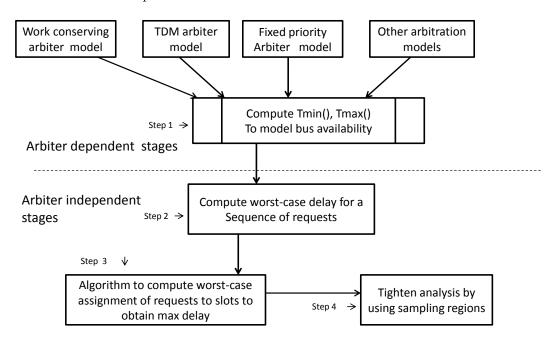

|          | 4.2                                                            | Overview of Approach                                                      |     |  |  |

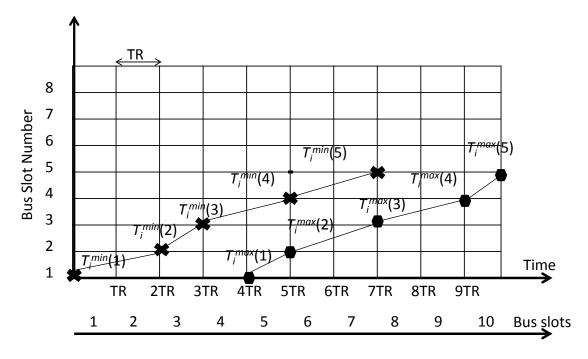

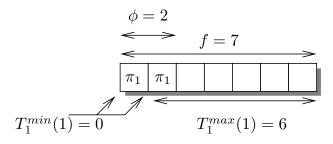

|          | 4.3                                                            | Step 1: Modeling the Availability of the Bus                              |     |  |  |

|          | 4.4                                                            | Step 2: Find the maximum cumulative delay for a given request-set mapping |     |  |  |

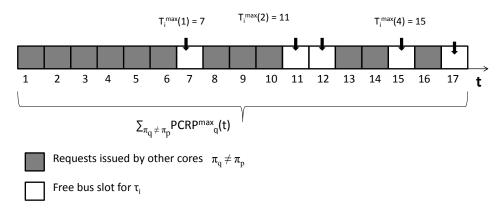

|          | 4.5                                                            | Step 3: Finding the worst-case assignment                                 |     |  |  |

|          | 4.6            | Step 4: Region-Wise Analysis                                | 125 |

|----------|----------------|-------------------------------------------------------------|-----|

|          | 4.7            | Related Work                                                | 129 |

|          | 4.8            | Experimental Results                                        | 130 |

|          | 4.9            | Conclusion                                                  | 133 |

| <b>5</b> | Bus            | Contention Analysis of Phase Change Memory based Multicores | 135 |

|          | 5.1            | Introduction to Phase Change Memory                         | 135 |

|          | 5.2            | Related Work                                                | 137 |

|          | 5.3            | Model of computation                                        | 138 |

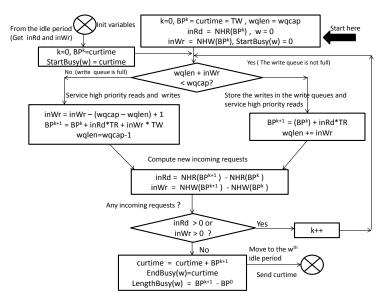

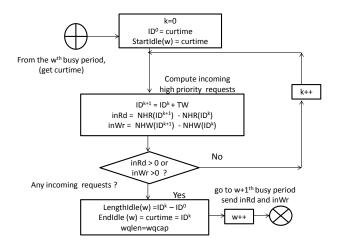

|          | 5.4            | An Initial Approach to the Problem                          | 141 |

|          | 5.5            | An Upper Bound on the external interference                 | 142 |

|          | 5.6            | Summary of the evaluations                                  | 152 |

|          | 5.7            | Chapter Summary                                             | 156 |

| 6        | NoC            | C Contention Analysis of Many Core Systems                  | 157 |

|          | 6.1            | Introduction to many-core systems                           | 157 |

|          | 6.2            | Related Work                                                |     |

|          | 6.3            | System Model                                                |     |

|          | 6.4            | Input Traffic Characterization Functions                    |     |

|          | 6.5            | Conceptual description of existing RC based methods         |     |

|          | 6.6            | Proposed method for tighter WCTT                            |     |

|          | 6.7            | The Branch and Prune Algorithm                              |     |

|          | 6.8            | A more efficient algorithm: Branch, Prune and Collapse      |     |

|          | 6.9            | Simulations and Results                                     |     |

|          | 6.10           | Conclusions                                                 |     |

| 7        | $\mathbf{The}$ | sis Summary, Reflections and Future Work                    | 193 |

|          | 7.1            | Summary of the work                                         | 194 |

|          | 7.2            | Limitations of current work and future directions           |     |

|          |                |                                                             |     |

# Chapter 1

# Introduction

"Technology is the campfire around which we tell our stories."

Laurie Anderson

### **1.1** Introduction to Embedded systems

A host of scientific inventions in the past decades have been vital in transforming the world from one inhabited by mankind to one which is strewn around with electronic and computing systems. The prevalence of these devices in our lives is so ubiquitous that it would not be far-fetched to state that we live in a world dominated by computing devices – from simple ones like a pre-set alarm in a cell-phone which heralds the dawn, pacemakers implanted within the human body to regulate and monitor heartbeats, to high end systems like space-ships which can literally transport us to another world. As an informed and curious species that we claim to be, an insight into these co-habiting devices is therefore warranted to understand their inner workings. Given the whole range of these systems, we shall focus on a specific set of these which are called "embedded systems".

Although it belongs to the broader category of systems called computing systems or computers, the key differentiator between embedded systems and other computers is the range of activities that they are designed for. In contrast to the more popularly known "computers" which are built with general purpose processors designed to carry out varying functions, the processor of an embedded system is pre-programmed to deliver a specific functionality. Although no standard and rigorous definition exists in literature, we shall refer to the following:

**Definition 1.** "Embedded Systems are electronic systems that contain a microprocessor or a micro controller, but we do not think of them as computers – the computer is hidden or embedded in the system." – Todd D. Morton [1]

Introduction

**Definition 2.** An embedded system is some combination of computer hardware and software, with either fixed or programmable capabilities, that is specifically designed for a particular kind of application device.

#### 1.1.1 Examples of embedded systems

It is interesting to know that embedded systems were primarily designed to cater to large, safety-critical applications like rocket and satellite control, energy production control, telephone switches, flight control. But with time, they have been employed in other fields thereby addressing a wider range of functionalities spanning transport systems (avionics, space, automotive, trains), electrical and electronic appliances (cameras, toys, televisions, home appliances, audio systems, and cellular phones), process control (energy production and distribution, factory automation and optimization), telecommunications (satellites, mobile phones and telecom networks), energy (production, distribution, optimized use), security (e-commerce, smart cards), health (hospital equipment, mobile monitoring), etc and have become indispensable to our daily lives. Given the aforementioned examples, we can without loss of generality say that embedded systems typically execute control functions, finite state machines, and signal processing algorithms. In addition they are also employed to detect and react to faults in both the computing and surrounding electromechanical systems besides manipulating application-specific user interface devices.

#### 1.1.2 Requirements of embedded systems

As seen above, given the multitude of larger systems that embedded systems reside in and the demand for integrating multiple functionalities into smaller compact systems, the resources available to these systems is highly constrained. It seems apt at this point to quote Peter Thompson, System Architect of Military and Aerospace, GE Intelligent Platforms [2]:

"It has become a recurring customer mantra: 'We want more capability than we had previously – but using less Size, Weight, and Power (SWaP) than the older systems used to."' Embedded computers typically have tight constraints on both functionality and implementation. In particular, they may need to conform to one or more constraints including size and weight limits, power consumption, satisfy safety and reliability requirements, guarantee real-time operation and be reactive to external events while meeting tight cost targets.

Koopman et.al [3] have described the specific requirements of embedded systems, which are summarized here. The size, weight and form factor constraints specifically hold for embedded computers which are physically a sub-component in bigger systems. Therefore, these constraints are inherently dictated by aesthetics, form factor requirements, or having to fit into limited spaces among other mechanical components. To optimize fuel usage and portability in the automotive domain, systems with smaller weight are desirable. Safety and reliability constraints are posed by systems which have obvious risks associated with failure. An example is mission-critical applications such as aircraft flight control systems, in which severe personal injury or equipment damage could result from a failure of the embedded computer.

For embedded systems that do not operate in a controlled environment, the main requirement is to continue operating in harsh conditions. Excessive heat is often a problem, especially in applications involving combustion (e.g., many transportation applications) or devices that are embedded in human beings (e.g., pacemakers). Additional problems faced by these systems is a need for protection from vibration, shocks, lightning, power supply fluctuations, water, corrosion, fire, and general physical abuse.

Most embedded systems must operate in real-time – the required behaviour must not only conform to the functional correctness, but also be delivered within preset time bounds. In many cases, the system design must take into account the worst-case performance. Predicting the worst case may be difficult on complicated architectures, leading to overly pessimistic estimates. Apart from all this, though embedded computers have stringent requirements, cost is always an important issue.

An embedded systems designer must therefore consider not only meeting the basic functional requirements like correct behavior but also address non-functional (more rightly called extra-functional) requirements like low power consumption, small form factor and weight, besides security, reliability and robustness. In addition, most embedded systems have to meet specific timing constraints and must deliver the correct behavior within a specified time limit – these systems belong to a specialized category of systems called *realtime embedded systems* (RTES). Such systems are a focus of this work and hence we shall explore them further in the next section.

### 1.2 Real-Time Embedded Systems

In simple terms, embedded systems which must adhere to certain temporal requirements and deliver the expected functionality within pre-defined time bounds are called "real-time embedded systems". In this section we shall discern in detail the meaning, categorization and properties of these real-time systems. In a real-time system, the correctness of the system behavior depends not only the logical results of the computations, but also on the physical instant of time at which these results are produced. The key differentiator is the dimension of time — a given response is deemed correct and useful only if it delivered in conformance with some temporal requirements. From a system perspective, a real-time system is essentially a set of subsystems i.e., the controlled object, the real-time computer system and the human operator or interfacing unit. It is reactive in nature i.e., it reacts to stimuli from the controlled object (or the operator) within time intervals dictated by its environment.

#### 1.2.1 Real-time Taxonomy

Most interactions (stimuli and responses) in real-time systems are recurrent in nature. Therefore these systems are typically modeled as finite collections of simple, highly repetitive entities or abstractions called *tasks* each of which releases a sequence of *jobs* at different rates depending on the nature of the application [4]. While the task is an abstraction, the jobs constituting it are the actual active instances of the task which perform the required actions by using the resources of the execution platform. In other words, a job is the unit of work that is scheduled and executed by the system.

#### **Definition 3.** A real-time task is a sequence of real-time jobs that are semantically related.

An example of the abstract nature of the task is the "maintain constant altitude" task for aeroplanes. This task will consist of a set of jobs that execute to allow the aeroplane to fly at a constant altitude. Formally we may define a job as follows:

**Definition 4.** A real-time job defines a basic request for execution. When such a request is made, C units of processor time must be allocated to this job over the next D time units. C represents the execution requirement, and D the relative deadline of the job.

Note that the deadline of a job is relative to its release time and hence is called the *relative* deadline. To re-iterate, a job is characterized by certain functional parameters which define its behaviour, temporal parameters to express its timing properties and constraints (like its deadline) and resource parameters which define its execution requirements.

#### 1.2.1.1 Classification based on job release patterns

Depending on the release patterns of the jobs by a task, we can classify tasks as follows [5]:

- Periodic tasks: Jobs of a periodic task are released by the task at constant intervals of fixed duration known as the "period" of the task.

- Sporadic tasks: Jobs of a sporadic task are released by the task at arbitrary points in time, but with defined minimum inter-arrival times between two consecutive releases.

- Aperiodic tasks: Jobs of an aperiodic task do not have any pre-defined bounds on their releases. In other words, an aperiodic task is a stream of jobs released by a task at irregular intervals, with no pre-defined pattern of release.

In this work, we focus only on *sporadic tasks*

#### 1.2.1.2 Soft, hard and firm real time systems

Every real-time system is associated with some timing constraints, called the *relativedeadline* in formal real-time terminology. The system may consist of one or more tasks that must be executed to deliver the required behaviour. The deadline denotes the time by which the each (job of a) task in the system must complete its execution in order to provide the desired output. In other words, the job(s) of the task must be also given the required resources for their execution i.e.,  $C_i$  time units of execution must be completed within  $D_i$  time units of their release. Failure to meet these deadlines can have varying repercussions depending on the system. Based on the different consequences of missing their deadlines, real-time systems are classified as soft, hard and firm real-time systems [6].

- Soft real-time systems: In these systems, missing a deadline leads to a degraded performance. The desired functionality (result), if produced after the pre-set deadline retains its utility (inspite of the degradation) and the system keeps functioning. Online transaction systems, airline reservation systems are examples of soft real-time systems. In other words, non-adherence to the timing requirements is tolerated to certain levels.

- Hard real-time systems: Systems in which missing the deadlines leads to a catastrophe, like loss to human life, fall under the category of hard real-time systems. The system moves to a "failed" state in such cases. In other words, given the dire consequence, non-adherence to the timing requirements is not acceptable in these systems. Industrial process controllers, pacemakers and air traffic control systems are examples of hard real-time systems.

- Firm real-time systems: In these systems, if the desired functionality (result) is produced after the pre-set deadline, the result has zero utility. Unlike hard real-time systems, even when a firm real-time task does not complete within its deadline, the system does not fail. The late results are merely discarded. In other words, the utility of the results computed by a firm real-time task becomes zero after the deadline. A video conferencing application which simply discards those frames which arrive after their deadlines, but continues processing the next frame is an example of a firm real-time system.

In this work, we focus only on hard real-time systems.

#### 1.2.1.3 Scheduling: Preemptive and Non Preemptive

We stated earlier, that the jobs of a task needs some execution resources from a processing element (processor). The scheduler is a specialized service of the operating system kernel responsible for deciding which job should be executing at any particular time. In other terms, the scheduler arbitrates the access to the processing element. The order of granting accesses to jobs of tasks is decided by the scheduling algorithm. Scheduling algorithms may be either preemptive or non preemptive. In non-preemptive scheduling, a job *must* be executed to completion once it starts execution, in preemptive scheduling, on the other hand, it is permitted that an executing job may be interrupted prior to completion and its execution may be resumed later [7]. The process of suspending the job of one task and activating the other involves a switch of the job execution context. The entire state of the suspended job must be saved to enable its seamless resumption at a later point of time. The delay in saving this context of a job leads to the context switching delay, which must be taken into consideration during analyzing the system.

#### In this work, for simplicity, we focus only on non-preemptive schedulers

To facilitate easy readability, in the rest of the document, we use tasks and jobs interchangeably to denote the unit of execution.

#### 1.2.1.4 Global and Partitioned Scheduling

If the host platform offers multiple processing elements, then jobs of a task can be scheduled to execute on any of them. The process of mapping jobs to the processing elements is called *task assignment*. Partitioned scheduling refers to a *static* task assignment in which each task is assigned to a processor and all of its jobs must execute on that processor. In contrast, a global scheduling policy allows for jobs of a task to migrate between processors and there is no strict affinity between a task and a processor. Task migrations have their own overheads, which are non-trivial to compute. Additionally, dealing with partitioned scheduling in itself in the context of this research poses numerous challenges and we believe that as a basic step, it deserves considerable research effort on its own.

In this work, we focus only on *partitioned schedulers*

#### **1.2.2** Desired properties of real-time systems

There are two main terms frequently associated with real-time systems: predictability and composability [8]. Real-time systems must exhibit *predictable* behaviour – the temporal behaviour of a system should be known in advance. Designing for predictability therefore involves analyzing the sub-systems that impact the temporal behaviour and assessing at design time, the various uncertainties that may arise due to different system states. This analysis is carried to derive specific bounds on the timing behaviour or performance, for example to find an upper bound on the time to access to a resource.

Secondly, another desirable property is that the components constituting a real time system must be *composable*. A composable system inherently provides temporal and functional isolation of tasks co-executed on it. As a result, the on line behaviour of tasks when run in conjunction with other tasks remains the same, as when run in isolation. This in turn helps ascertaining at design time, the temporal properties of tasks by analyzing the task in isolation and avoids the problem of analyzing the impact of other sub-systems. As an additional benefit, components with composable properties can be individually developed and tested, which reduces non-recurring engineering costs.

Since the precision of the results and the efficiency of the analysis methods are dependent on the predictability of the execution platform, they must be designed to cause minimal variation of the instruction timing, cause no interference between components provide predictable behavior and provide comprehensive documentation to help in the derivation of reasonable estimates on the execution behaviour [9].

Next we shall introduce the standard notations commonly used in the real-time system literature.

#### 1.2.3 Notations used to model real-time applications

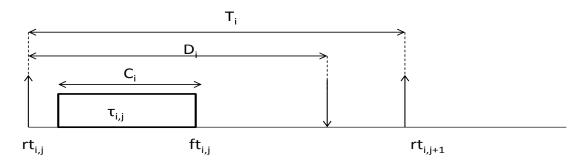

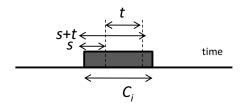

Figure 1.1: Illustration of the job parameters. Upward arrows indicate job arrivals and downward arrows indicate job-deadlines

A real-time application is modeled as a static set of n tasks  $\tau = \{\tau_1 \dots \tau_n\}$ . Each task  $\tau_i$ releases a sequence of k jobs  $\{\tau_{i,1} \dots \tau_{i,k}\}$ , where k is a non-negative number and potentially  $k \to \infty$ . Each task  $\tau_i$  is characterized by a three-tuple  $(C_i, T_i, D_i)$ . The term  $C_i$  is used to denote an upper bound on the execution time required by a job of task  $\tau_i$  to complete its required functionality, without being interrupted and is called the worst-case execution time. The symbol  $T_i$  denotes the frequency at which jobs of task  $\tau_i$  are released in the system. While  $T_i$  is used to denote the period for periodic tasks, it is used to denote the minimum inter-arrival time for sporadic tasks. The relative deadline denoted by  $D_i$ , is the time by which  $\tau_{i,j}$  (this notation means the  $j^{th}$  job of task  $\tau_i$ ) must complete its execution.

Depending on the relation between the deadline and the period of tasks, a task set  $\tau$ , can be categorized as follows.

**Definition 5.** An implicit-deadline task-set is characterized by the property that the relative deadline of each task  $\tau_i$  is equal to its period, i.e.,  $(D_i = T_i)$ .

**Definition 6.** A constrained-deadline task-set is characterized by the property that the relative deadline of each task  $\tau_i$  in the task set is no greater than its period i.e.,  $(D_i \leq T_i)$ .

**Definition 7.** An arbitrary-deadline task-set is characterized by the property that there is no such constraint on any task  $\tau_i$  in the task-set, that is  $D_i$  can be less than, equal or greater than  $T_i$ .

In this work, we focus only on *constrained-deadline task-sets*

Each job  $\tau_{i,j}$  becomes ready to be executed at release time  $rt_{i,j}$  and continues until finishing (or completion) time  $ft_{i,j}$ . The duration of this time interval is said to be the response time  $r_{i,j} = ft_{i,j} - rt_{i,j}$  and the response time,  $R_i$  of task  $\tau_i$  is defined as being the maximum response time of all its jobs ( $R_i = \max_{j=1}^k (r_{i,j})$ ). The response time of a job denotes the time between its arrival and its completion and the worst-case response time of a task is the maximum amongst the response time of all the jobs released by the task.

#### 1.2.3.1 Timing Parameters

As noted earlier, meeting deadlines is especially key for hard real-time systems, as failing to do so may result in fatal consequences. The notion of meeting deadlines further translates to the fact that each task must deliver its functionality within the given deadline. A task typically shows a certain variation of execution times depending on the input data or different behavior of the environment. The upper bound on the execution time is called the worst-case execution time (WCET) [10]. Formally we can define the WCET as follows:

**Definition 8.** "The worst-case execution time of a task indicates an upper bound on the execution time amongst all of its job releases, assuming that its execution is not interrupted".

Note the term "upper bound" in the definition. It is very inefficient, or even impossible to obtain the *exact* maximum value by simulating all possible combinations of input parameters [9]. This is due to the fact that the execution time is dependent on the current state of the environment and the inputs. For example, the execution time of a program is dependent on the speed of the processor it is executed on, the speed of the memory, communication channels, the current input to the program, the state of the caches and various other factors. The execution times of two consecutive program runs may differ due to changes in the cache states, inputs, changes in processor speed (owing to some background power management modes) and a host of other factors.

Therefore, an upper bound on the maximum value called the worst-case execution time is computed. These computed values have to be safe, in that they must not underestimate the actual upper limit. Moreover, they should be tight, i.e. they should be as close as possible to the exact maximum values (which in general are not computable). Similar to the WCET, another key parameter is the worst-case response time (WCRT) of a task.

**Definition 9.** The response time of a job denotes the time between its arrival and its completion and the WCRT of a task is the maximum amongst the response time of all the jobs released by the task.

The computation of parameters like the WCET and WCRT is a part of the process referred to as the *timing analysis*. The aim of timing analysis is to give an estimate for the time a given program will take to execute under all feasible system states. Execution time estimates are used in real-time systems development to perform scheduling and schedulability analysis, to determine whether deadlines are met for tasks, to check that system-features like interrupts complete their routines in bounded times, etc.

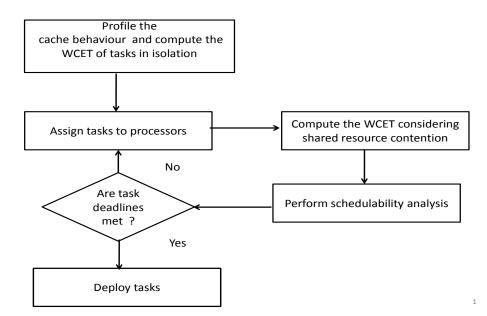

An offline analysis of the task behavior to determine the key parameters like the upper bounds on the execution time or the WCET is vital to ensure compliance with the timing requirements of the system. Hence it is equally important to understand the parameters which can influence it and the challenges that the deployment environment poses in deriving such upper bounds. In the context of the task deployed on a computing platform, the variations in the execution time are greatly influenced by the platform's architecture. For a holistic analysis, understanding the execution environment is thereby of vital importance. In the later part of the chapter, we will focus on the processor platforms on which these real-time systems are hosted, but before that it is important to understand the driving factors behind the choice a given platform. For this, an insight into the recent trends in the embedded systems is warranted and is explained in the following section.

### **1.3** Paradigm shifts in the design of embedded systems

#### **1.3.1** Shift from federated architectures to integrated architectures

The ever-increasing computing demands of emerging embedded applications has driven designers to shift from federated architectures towards integrated architectures. A *federated architecture* is characterized in that every major function of an embedded system is allocated to a dedicated hardware unit [11]. In an embedded system with evolving functionalities, this implies that adding a new function is tantamount to adding a new computational node.

As a classical case, consider the automotive domain: the number of Electronic control units (ECUs) in cars has doubled over the last decade, with upto 70 to 100 ECUs in high-end vehicles [12]. Traditionally, system designers have followed the "one function per ECU" paradigm, which scaled for systems with few ECUs in terms of the communication architecture (wiring), power consumption and maintenance costs. However with increased functionality required in applications (like navigation and infotainment features in automotive systems), the number of ECUs required increased significantly. To add to the complexity, fault-tolerance, a feature highly desired in some embedded systems, is achieved by provisioning redundant units leading to a further significant increase in the number of nodes and networks.

The increased efforts required to manage this increased complexity, while keeping power consumption at an acceptable level has led system designers to the *integrated* architecture which is based on the principles of adopting a shared computing, communication and I/O resource pool that is partitioned for use by multiple system functions [13]. The avionics field has been adopting this design paradigm which is known as the *Integrated Modular Avionics*

(IMA) architecture. The IMA concept, which replaces numerous separate processors with fewer, more centralized processing units, has witnessed significant weight reduction and maintenance savings in the new generation of commercial airliners. Boeing said by using the IMA approach it was able to reduce 2,000 pounds off the avionics suite of the new 787 Dreamliner, versus previous comparable aircrafts [13]. In alignment with these design requirements, multicores have emerged as a natural choice for system designers. They facilitate the integration of multiple functionalities onto one chip and provide major cost and performance benefits besides reducing the communication infrastructure and also the number of units to be maintained. Considering the example of the automotive domain it may be said that depending on the integration levels, future vehicles may have around 10 to 20 multicore domain control units instead of having 100 ECUs. Applications with high computing demands like navigation, telematics and infotainment can be co-hosted on these chips and can leverage the potential of these multicore platforms. To cater to the stringent needs of embedded systems, chip vendors have developed multicore systems with reduced SWaP (size, weight and power) properties. As a result, multicores have been ubiquitously used in the field of embedded systems.

Besides the shift to integrated architectures, another popular trend has been the adoption of Commercially available off the shelf (COTS) components. The next section provides an insight into the factors behind this shift.

#### 1.3.2 RTES: The shift towards using COTS components

In-lieu of the strict timing requirements of hard real-time systems, real-time embedded systems were traditionally assembled from scratch using custom built hardware and software components, specifically designed for such systems. The entire product development cycle was long and expensive especially when used in massive systems (e.g. aircrafts): Each of the individually developed components had to be designed, developed and unittested and then finally integrated with the rest of the system. But with time, products got more complex and there has been a push towards using COTS components for their development.

The key driving factors for the adoption of readily available COTS components, rather than the in-house development of the entire system have been presented in [14]. For completeness, we re-state these factors here. Firstly, the growing competition among product designers to deliver more reliable systems in shorter time frames has driven them towards using COTS components. Secondly, the demand for larger and more complex solutions, cannot be effectively implemented in a timely manner by a single vendor, pushing designers to look at readily available components in the market. Also, product designers wanted to harness the benefits of highly available, reusable and fully tested COTS components. COTS component design has matured over the times and currently there is an increased degree of standard compliance among COTS products. This has been another major driving factor for their adoption, since the adherence to standards-based development enables reduction of product integration time. Also, the increasing research in better software component "packaging" techniques and approaches have helped designers in the integration process and debugging any subsequent problems.

The adoption of COTS-based multicores in particular was also driven with the fact that previously distributed functionalities of multiple cores are now available as a single chip. In earlier systems in which functionalities were deployed in isolated chips, inefficiencies of working with multiple support environments and programming models led to a longer timeto-market and increased long-term support costs. Building and maintaining systems with multiple chips, power supply units, memories, and I/O interfaces to support the different processors adversely impacted system component manufacturing and maintenance costs.

Although COTS components provide plenty opportunities for embedded system designers, they are not without their own demerits.

# 1.3.3 Problems with adopting COTS components for designing real-time systems

COTS components are already used in real-time systems with low criticality (also called soft real-time systems), but they are not yet typically employed for hard real-time. The reason is that COTS components are primarily designed towards increasing the average case performance. In contrast, the key requirement for most hard real-time systems are components that collaborate together to provide *predictable* and reliable behavior. The components must provide enough documentation to derive tight upper bounds on the required parameters. But in existing COTS systems, most often only a brief description of its functionality is provided. Also, these components do not carry any guarantee of adequate testing for the intended hard real-time system environment. For example, a processor manual may report that the average time to access main memory is "x" cycles – but what is required is the worst-case estimates. Further-more only a limited description of the quality of the component is provided and the quality must be re-assessed in relation to its intended use. In most cases, the designer does not have access to the source code of the component and this inhibits easier modifications to the current design – Many COTS components are therefore "black boxes" without their source code or other means of introspection available.

Next, let us gain an insight into the COTS-based computing platforms which are employed in embedded systems.

### **1.4 Computing Platforms**

This section defines a multicore processor, delves in the architectures and cites examples of commercially available systems.

#### **1.4.1** Introduction to Multicore systems

With the increase in the number of functionalities provided by embedded systems, platforms that provide high computational capabilities while consuming less power together with a reduced form-factor have been highly sought after by system designers. In the past decades, chip designers addressed these demands by developing faster and faster uniprocessors by increasing the raw clock speed. However the techniques in designing memory systems did not catch up with the CPU speeds as memory access latencies were non-negligibly high leading to large processor stalls. Latency hiding techniques were then employed by designers by building in concurrency within the processor via instruction level parallelism techniques including out-of-order execution, pipelining and branch prediction. The aim was to reduce process stall times (due to memory fetch delays) and thereby maximize the processor utilization. The trend of increasing CPU speeds hit a threshold and could not scale further owing to the physical and the electromechanical limits imposed by increased transistor scaling, power requirements (the power wall), and heat dissipation [15], [16]. Monolithic unicores reached a plateau of clock frequency and chip manufacturers shifted towards the design in which multiple, sleeker, simpler, slower processors were fabricated on a single chip, which collectively not only enhanced the resulting computational power but also did so at a lower watt/instruction per cycle (IPC). These systems are now commonly referred to as as *multicore processors* or *multicore systems* or simply *multicores*. Some of the current multicores like the Niagara processor from Sun Microsystems or Intel's Larrabee [17] processors have simple processors with in-order execution.

A multicore processor is generally defined as an integrated circuit onto which two or more independent processors (called cores) are fabricated. An informal definition from Techopedia [18] is presented here:

**Definition 10.** "Multicore refers to an architecture in which a single integrated circuit called a die, is used to package or hold multiple processors. The objective is to create a system that can complete more tasks at the same time, thereby providing better overall system performance."

Note that this term is distinct from but related to the term multi-CPU, which refers to having multiple CPUs which are not attached to the same integrated circuit.

#### 1.4.2 Example Multicore systems

There is no doubt that the multicore transition in the microprocessor world is all but complete. The road maps of all the leading chip vendors indicate that their future products incorporate architectures that feature multiple CPU cores on the same chip. Example Multicore processors from different chip vendors include [16]:

• Intel: Core Duo, Core 2 Duo, Core 2 Quad, Core i3, i5, i7, i7 Extreme Edition family, Itanium 2, Pentium D, Pentium Dual-Core, Polaris, Xeon

- AMD: Opteron, Phenom, Turion 64, Radeon, and Firestream

- IBM: POWER4, POWER5, POWER6, PowerPC970, Xenon (X-Box 360)

- Azul Systems: Vega 1, Vega 2, Vega 3

- Cavium Networks: Octeon; ARM: MPCore

- Freescale Semiconductor: QorlQ; Analog Devices: Blackfin

**Classification of multicore systems** Based on their characteristics of the instruction sets and processor speeds, these systems are categorized as identical, uniform and heterogeneous multicores. Identical multicores, as the name suggests are symmetrical in the instruction set architecture (ISA) and the speeds of the processors. In a uniform multicore setting, each of the cores have the same ISA, but may be executing at different speeds. In contrast to the above, the cores in a heterogeneous system may have a different ISA and may be specialized for different functionalities.

In this thesis, we consider *identical* multicore systems only.

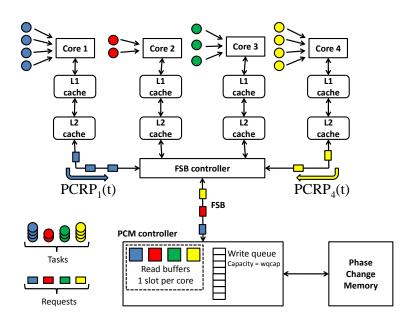

#### 1.4.3 Overview of a typical multicore

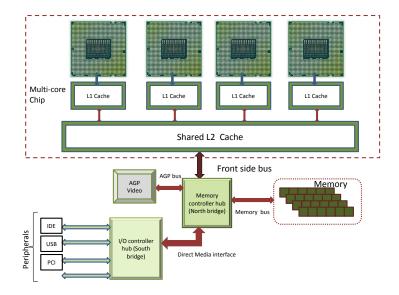

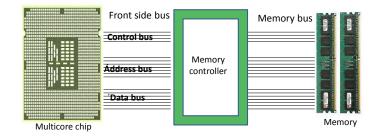

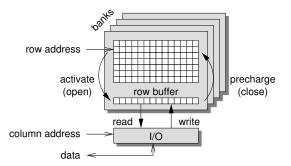

The architecture of a typical COTS-based multicore system is illustrated in Figure 1.2. Although the figure is aligned to the Intel processor [19], but it is for illustration purposes only and the discussion will cater to the majority of the multicores in general. It depicts a single chip which contains 4 processing elements or processors (or central processing units (CPU)) and 2 levels of caches – the L1 cache (private to each core) and a shared L2 cache connected over a communication channel to access the main memory. A tiered memory hierarchy is generally employed with smaller faster memories (caches in this context) which are integrated on the same chip and a larger and slower external off-chip memory. These caches are employed to hide the latency in accessing the slower large main memory. The rationale behind the need for caches is that frequently accessed data must be kept closer to the processing source or "cached", to reduce processor stall cycles. On the first access to a particular address (the cache is looked up and the data is not found therefore called a "cache miss"), the required data or instruction is fetched from the off-chip main memory and a copy is also stored on the local caches. On subsequent accesses to the same address, the cache is checked and if the data is found (called a "cache hit"), it is retrieved from the cache itself without incurring the (high) latency to fetch the data all the way from the memory to the processor. This is possible since most programs exhibit some kind of temporal and spatial locality. In most multicore designs, each core of a multicore chip has a private level-1 cache and may share a level-2 cache (and more levels down like a level-3 cache).

The multicore chip is connected to the memory controller (called the North-Bridge (NB) in Intel terminology) over an interconnection network. In our example COTS-based architecture depicted in Figure 1.2 this interconnection network is a single shared bus, usually called Front-Side Bus (FSB). The FSB is the electrical interface that connects the processor to the main chipset (which consists of integrated chips like the memory and I/O controller chips). The FSB is also referred to as the processor system bus or simply the system bus. All interrupt messages, memory, coherency traffic and I/O transactions flow between the cores and the chipset through the FSB. Since the FSB is the only path from all the cores to the memory, in case of simultaneous requests from different cores, it has an additional responsibility to decide (or "arbitrate") the order of request transmission. This is done using an arbitration mechanism, like a round-robin mechanism, a priority driven mechanism or other mechanisms. To ensure low waiting times, most bus arbitrate are "work-conserving": If there is a request to be served, the bus has to serve it and cannot be idle.

We shall discuss the arbitration policies in the next chapter.

Figure 1.2: A typical COTS-based multicores architecture.

It is important to note that in this model, all the cores have the same view of the memory and requests issued by any of them (in isolation) will take the same time to reach the memory. Such a model conforms to a Uniform Access Memory (UMA) model and will be followed in the rest of the analysis of multicore systems. The North-Bridge typically handles communications between the CPUs, the system main memory (RAM), the Accelerated Graphics Port (AGP) bus to the AGP video cards and the South-Bridge (SB). The main memory is thus shared between multiple entities over the North-Bridge, which we shall henceforth refer to as "agents", i.e., the main agents that access the system memory are the multicore chip, the graphics controller and the SB unit. The communication between

the main memory and the other agents is handled by a memory controller and a memory arbiter, both directly incorporated into the North-Bridge. Generally, a graphics controller is connected to the NB (or is sometimes integrated into the NB as well depending on the chipset design).

The South-Bridge, often referred to as the I/O Controller Hub, handles communication with the peripherals such as the hard-disk, keyboard, printer, etc., over a variety of buses like the PCI) and PCI express. The peripherals can be connected in various ways depending on the chipset design. Typically, the SB is connected to the NB via a Direct Media Interface (DMI) channel. All the Direct memory access (DMA) traffic (arising from the peripherals) is also channeled through the south bridge.

Our multicore model: single shared bus with private caches only

After gaining an overview on the architecture of a multicore which clearly shows the presence of shared resources like the shared bus, it is important to understand their impact of execution behaviour of tasks hosted on them.

#### 1.4.4 Contention for the shared hardware resources in multicore systems

In contrast to the uniprocessor design in which a single core had access to the cache, the bus and the memory controller, the same low-level hardware resources are shared amongst different cores in a multicore system. Resources are mainly shared to minimize cost, energy, and increase the performance, while conforming to the design parameters of the end product, like the size, weight and power requirements. The problems in the timing analysis of multicores can be mainly attributed to the interference on these shared resources.

Consider a scenario in which there are several tasks assigned to each core in a multicore system and all the cores are active. Under such a scenario, when a specific task suffers a cache miss and has to access the main memory over an interconnection network (like the shared memory bus), its request may be blocked by the requests issued from tasks executing on the other cores. Specifically, the core hosting that task is stalled, waiting for the data to be fetched. As the number of cores that use the same front side bus (FSB) increase, the traffic on the FSB increases and this shared bus becomes the main bottleneck. This means that the processor needs to stall for a longer time, waiting on the data and hence more processor cycles are wasted. The extra delay incurred due to the bus contention is non-negligible and hence the resulting execution time of a task can be significantly increased. It was shown by Zuravlev et.al [20] that FSB contention accounts for as much as 60%- 80% of the performance variation that tasks experience on multicore processors. Additionally, in some multicore systems, the caches are shared among the cores; this further exacerbates the problem; tasks running simultaneously on two different cores may evict each other's cache lines, thereby increasing the number of cache misses, leading to additional requests to memory and adding to the traffic on the shared bus. Hence, any timing analysis for hard real-time systems in the context of multicore systems cannot ignore the impact of the shared hardware resources. The requesters of a shared resource may often access the resource at arbitrary times, which are difficult to discern at design time. As a result, different access sequences may result in different states of the resource. The combination of different resource-states and access patterns complicates the analysis. The lack of spatial and temporal partitioning and the barely analyzable worstcase timing behaviour of performance-enhancing features render the validation of claims about the dependability and correct timing of applications on current powerful multi-cores extremely difficult to defend and prove.

#### 1.4.5 From multicores to many-cores

Just as the technical community was getting used to the idea of multicore processors in systems on chips (SoCs), advancements in semiconductor technology propelled chip designers to further push the limits. On a casual note it may be said that, processor cores are replacing transistors as the building blocks of the current computing hardware. The multicore is becoming *many-core*; the number of processor cores closely coupled at the hearts of SoCs is rising from 4 to 8, 16 and currently chips with 256 cores are already present in the market. The Tile-Gx72 with 72 cores from Tilera [21], Kalray with 256 cores [22], Epiphany with 64 cores from Adapteva, Intel Xeon co-processor [23] with 60 cores and the 48-core Single-Chip-Cloud computer [24] are just some examples of such many-core architectures. These systems, like Kalray's MPPA (Multi-Purpose Processor Array) have been optimized to address the demand of high performance, low power embedded systems and therefore these architectures must be analyzed. The next section provides an overview of such an architecture.

## 1.5 Overview of a typical many core system

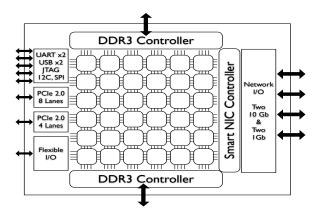

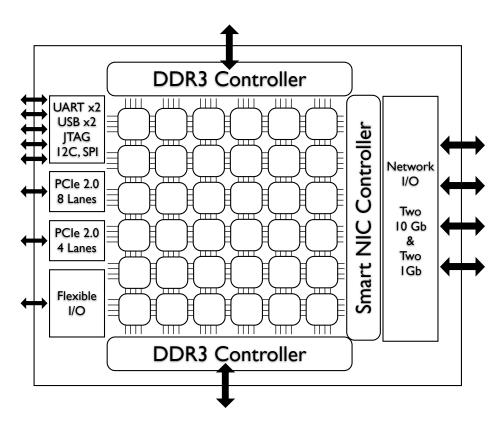

Figure 1.3: Tilera architecture. (Diagram taken from [21])

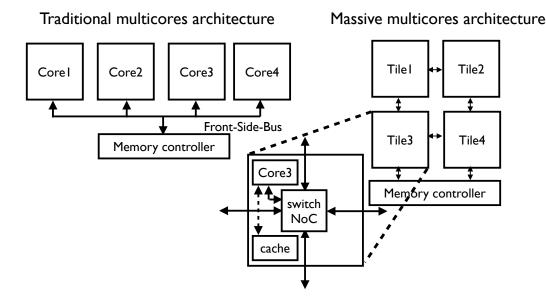

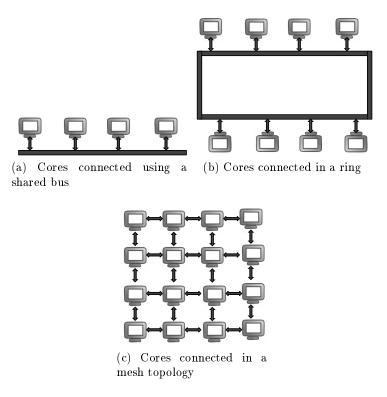

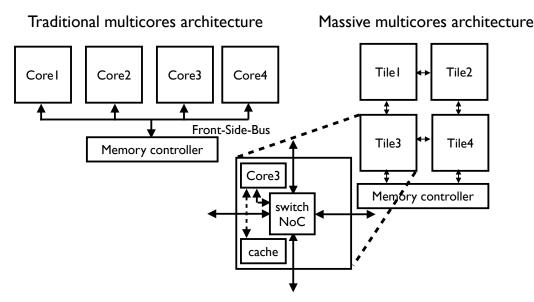

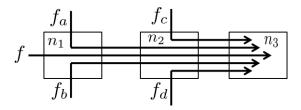

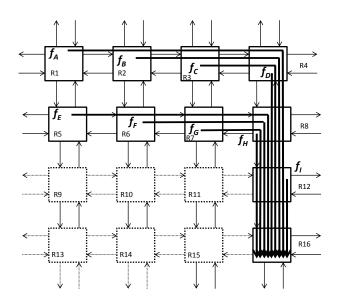

Figure 1.3 illustrates a many-core system based on the Tilera Platform. Without loss of generality we shall discuss this particular platform to gain the basic understanding. As seen in the figure, the architecture of a many-core system is visibly different from multicores, considering the number of cores, the interconnection mechanism between different cores and the positioning of the peripherals and the memory controllers. It was seen that the traditional shared bus/ring architecture (c.f. left plot of Figure 1.4) that serves as the interconnect between the cores cannot not scale beyond some number of cores (typically 8 cores is the limit). The shared bus, instead becomes a bottleneck leading to substantial increase in the access time to the off-chip memory thereby offsetting the benefits of high computing power provided by the cores. The increase in the number of cores forced a shift in the earlier design paradigm towards a more scalable interconnection medium: the Network on Chip architecture [25]. Longer wires connecting all the cores were replaced by routed interconnects using switches. This design conforms to the distributed architecture, while still being integrated on a single die.

Figure 1.4: Multi-core vs. many-core architectures

**Organization of the cores:** One of the base principles of the many-core technology is the division of the processing elements (cores) into "tiles" interconnected by a NoC. Each tile is thus a basic modular unit, composed of a processor core, a private cache subsystem and a network switch and these tiles are homogeneous across the entire chip. The tiles are laid out in a two dimensional grid and the switch connects the tile to its neighboring tiles located in the cardinal directions, thereby forming a 2D-mesh (c.f. right plot of Figure 1.4). The NoC serves as a communication channel among the cores and between the cores and other off-chip subsystems, e.g. the main memory. The off-chip subsystems like the peripherals and the main memory are connected to the tiles on the periphery of the grid. Note that absence of a centralized single shared cache in this architecture, since it is distributed across the tiles.

#### 1.5.1 Contention of shared resources in NoC based many-cores

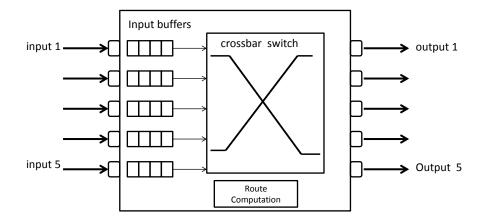

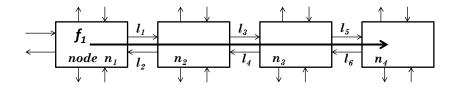

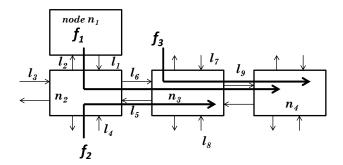

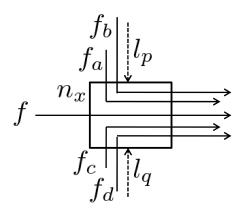

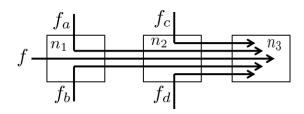

Figure 1.5: Illustrating the switch, the physical links and buffers

Figure 1.5 gives some more details regarding the switch, in which the 5 physical links incident on the input ports represent communication channels from each of the cardinal directions connecting the given tile to its neighbors in the north, south, east and west direction and a fifth link that facilitates the connection to the core present on that tile itself. Similarly, the data leaves the switch from the output links. In this diagram we have illustrated a single set of buffers which hold data from a given input port — in practice there many be many buffers and therefore many *virtual channels*. The buffers act as storage areas of finite capacities or placeholders for data in transit, until the required output port (and the corresponding output link) is busy. In this work, we assume a single virtual channel. As seen in this diagram, the main shared resources in a NoC are these buffers and the physical links.

At any given time, tasks running on different cores may release packets over the network independently and asynchronously. All the packets are transmitted over the same underlying interconnection network and share the available network resources. When several packets try to access the same resource at the same time and if resources are insufficient, it leads to a contention — for example, a router in the network may be able to only serve one packet and suspend the others based on some arbitration policy. Additionally, a packet that is blocked at one link, can in-turn block other packets waiting on previous links and the effects can cascade leading to a congested network, thereby causing a significant delay in the packet's traversal time. Thus the time to transmit a packet depends on the current load of the network, which in-turn is determined by the number of packets generated by the tasks executing on the other cores. Other factors like the routing mechanism employed also impacts the traversal times as it influences the path taken by the packets to reach their destination — this in-turn decides whether they would directly or indirectly block the analyzed packet by contending for the same resources.

To summarize, the number of parameters contributing to the unpredictability combined with the large number of cores poses a challenging problem to designers aiming to determine an upper bound on the traversal time of a (message/memory/ IO) packet. This traversal delay can be large and can increase the execution time of the task issuing these packets. If real-time tasks are to be hosted on such many-core platforms, pre-assessing this delay at design time is crucial. In this thesis we aim to compute such an upper bound which is referred to as the worst-case traversal time (WCTT).

We are now equipped with the necessary background to understand the problems addressed in the thesis.

## 1.6 Problems addressed in this thesis

At the level of the processor, a task is generally a sequence of instructions which operate on some data. Once the data is available to the processor, it performs the required computations. The instructions and data reside in some level of memory (L1 cache or L2 cache or the main memory itself) within the memory hierarchy. Therefore, the total execution time of a task can be demarcated as the computational phase and the communication phase, between which an executing task keeps alternating. Then a simple way to compute the execution time is given by,

Execution time = time for computation + time for communication

- The computational phase is the time during which the task consumes resources of the processor or the *on-core* resources like access to the arithmetic logic units for computations. In a multicore/manycore system, for a task that is assigned to a processor, this component of the execution time is *independent* of the tasks executing on the other cores.

- The communication phase represents the time to fetch the required instructions and data from the memory, write the data back to memory or the time to communicate between the cores. In this phase, the task consumes resources off the chip, which include the bandwidth available on the interconnection network which connects the processing elements to the memory. In a multicore system, in which these off-chip resources are shared by the other cores, the communication delay *is dependent* on the utilization of the same resources by tasks executing on the other cores. Similarly in a many-core system the time to send or receive data across the shared interconnection network is dependent on the data traffic introduced by other cores.

Each data transfer constitutes a request for the interconnect mechanism (the shared bus in multicores or the interconnected mesh network in many-cores). Consider task  $\tau_i$  which

needs  $C_i$  processing units (its WCET in isolation) and generates  $N_i$  requests. Assume that request *i* needs  $w_i$  units to be served, which implies that the core is stalled for the same time, due to which the final execution time of the task in contention  $C'_i$  is given by

$$C'_{i} = C_{i} + \sum_{i=1}^{N_{i}} w_{i} \tag{1.1}$$

In the broader context, the main aim of this thesis is to derive the delay incurred by the executing task due to contention for the shared interconnect. Towards this aim the thesis, explores related problems and subproblems, and we focus on three main areas:

- 1. Analysis of the impact of the shared bus on the execution time of a task in multicore systems.

- 2. Analysis of the impact of the interconnection network on the traversal time of a packet in many-core systems.

- 3. Analysis of multicore systems considering memory systems like Phase Change memory in which the read and write latencies differ to a great extent.

We have enlisted the assumptions earlier, but will re-state them here for completeness.

#### **1.6.1** Bus Contention Analysis of multicores

Problem statement: Given a multicore system, in which cores do not share cache space, tasks are assigned apriori to all the cores and given the execution time of each task in isolation, determine an upper bound on the increased execution of a task when it is run in conjunction with other tasks co-executing on other cores. This analysis takes into consideration the contention between co-executing tasks on all the cores for the single system bus. The analysis assumes that tasks are sporadic, non-preemptive and the scheduler does not allow tasks to migrate between cores. The main aim of the problem is to arrive at a unified framework for computing the WCET of a task, for any given arbitration mechanism employed by the bus. The main problem is tackled by solving the following sub-problems:

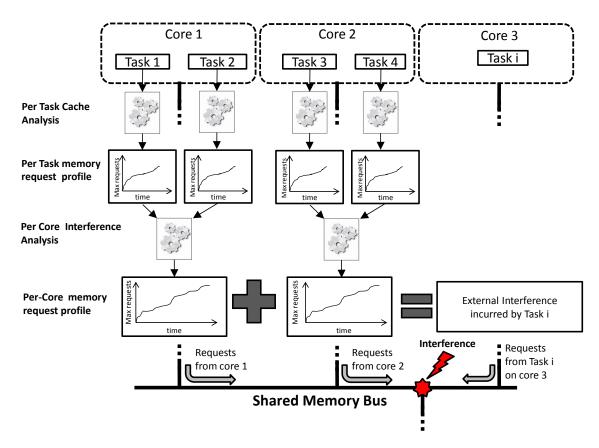

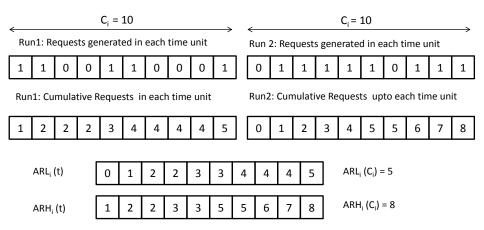

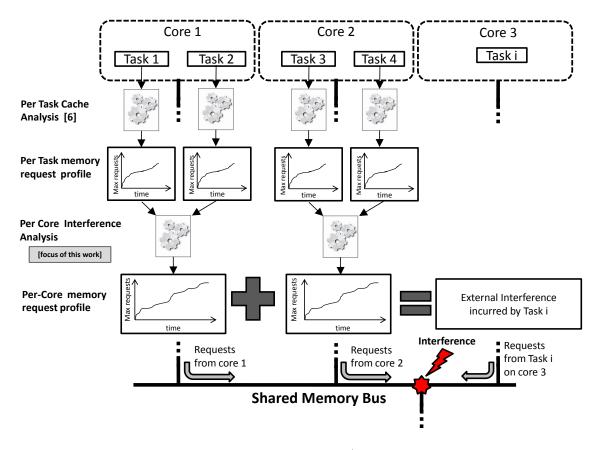

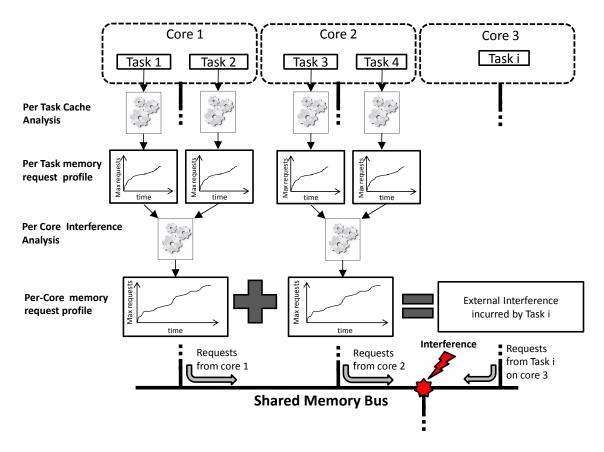

- To analyze the delay caused due to contention on the bus on a given task, a prerequisite is to analyze the memory traffic injected by tasks executing on other cores. Hence the first problem to be solved is *modeling the memory access pattern of tasks* and deriving the maximum traffic generated by the *tasks* in a given time interval.

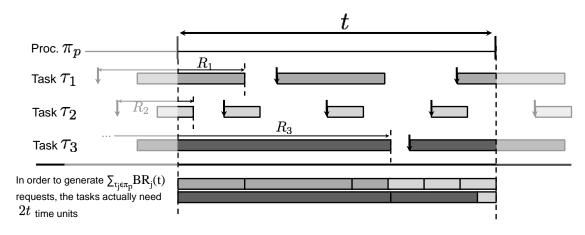

- 2. Given the memory profile of every task on a core, the next problem to be solved is deriving the maximum traffic generated by the *cores* in a given time interval. Being able to do so will provide an abstract interface that takes into consideration all possible patterns of task arrivals and returns the maximum traffic that can be injected into the shared bus by any core in a given time interval.

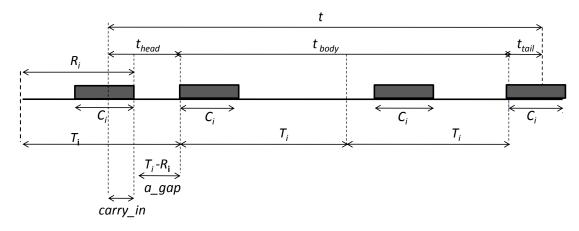

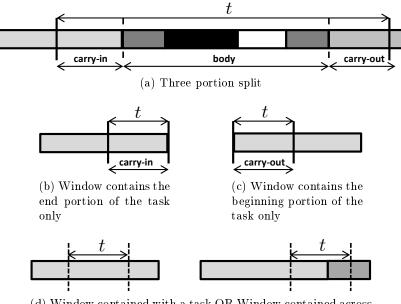

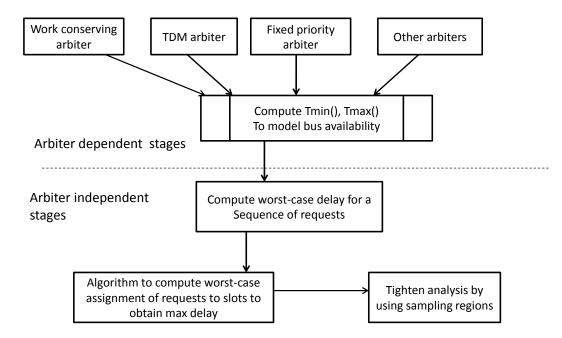

- 3. A pre-requisite to analyze the maximum delay incurred by a request on the bus is to understand the underlying arbitration mechanism. The order of servicing the requests by the bus is based on its arbitration mechanism and the next step in the analysis is *modeling the availability of the bus*- to demarcate the time intervals during which the bus is busy handling traffic (from the contending tasks) and the time at which the bus is potentially available to serve the requests of the analyzed task.

- 4. The next problem is to develop a method of scheduling the requests (of the analyzed task) on the available free bus slots with the objective of maximizing the waiting time of each request and thereby computing the maximum delay that the task incurs. It is very difficult to derive at design time, the exact release time of every request and we can only derive the number of requests that can be released over a period of time. Give this coarse grain request distribution, we must be able to schedule requests in a manner to generate the worst-case delay.

#### 1.6.2 Network contention analysis of many-core systems

Problem statement: Given a many-core system in which the cores are arranged in a mesh topology, and communicate with each other via an interconnection network, and data is assembled into packets, compute an upper bound on the traversal time of the packet, considering the contention for the finite links and buffers on the interconnection network. The computed parameter is referred to as the worst-case traversal time (WCTT) for a NoC based many-core system. The main problem is tackled by solving the constituent sub-problems.

- 1. The first important problem is to characterize the application's flow pattern and compute the delay incurred by a packet in isolation.

- 2. A packet may incur delay at each intermediate router when contending with other packets issued by other flows. The next problem is to formulate a delay analysis by considering the routing and switching mechanisms employed by the interconnection network.

- 3. Given that packets may originate from different flows in different orders, a method to construct different flow sequences (scenarios) in order to generate that sequence which can pose the maximum delay to the analyzed packet, is warranted.

- 4. To avoid an exhaustive enumeration during the generation of these scenarios, an important concern is to reduce the number of investigated scenarios. This is done by applying packet release constraints to the scenarios and pruning infeasible scenarios.

Other major design issue when many-core systems are concerned, is providing scalable mechanisms that can cater to systems with large number of cores and can provide tight bounds, efficiently even when the network is heavily loaded.

#### 1.6.3 Analysis of Phase Change Memory (PCM) based multicores

A significant part of the total delay incurred in serving requests of a given task, can be attributed to the latency imposed by the memory sub-system. Unlike the timing analysis of multicores where we consider a system for which the memory latencies for a read and write request are the same, newer memory systems with asymmetric latencies like Phase Change Memory (PCM) have been proposed. PCM is non-volatile, unlike Dynamic Random Access Memory (DRAM), consumes lesser power and is sought after by embedded system designers. We discuss more about PCM in detail in Chapter 5.

However, due to the intrinsic properties of PCM [26], the time to complete a read and write operation differs greatly; completing a write operation may take upto 10 times the time to complete a read request. If reads and writes are treated in the same manner by the memory controller, it may lead to huge processor stall times, especially during very slow write operations. To mitigate these delays, researchers have proposed different scheduling policies to be adopted by the memory controller: like prioritizing reads over writes in order to reduce program stall times. It is interesting to explore such memory systems with asymmetric read and write latencies and as a part of the thesis we also analyze such a system for its temporal behaviour.

Problem statement: Given the WCET and the memory profile of a task in isolation, compute the increase in the WCET when it runs in conjunction with other tasks deployed on a multicore system in which Phase Change Memory (replaces Dynamic Random Access Memory and) forms the main memory.

In addition to the analysis of the shared bus, the problem consists of analyzing the PCM controller. This problem involves modeling the memory controller, computing the bus availability for the analyzed task and then finding a tight upper-bound on the cumulative delay that memory requests may incur in the FSB and PCM controllers, considering that the time to serve a write request is much higher than the time to service a read request. We shall revisit this problem in detail in Chapter 5.

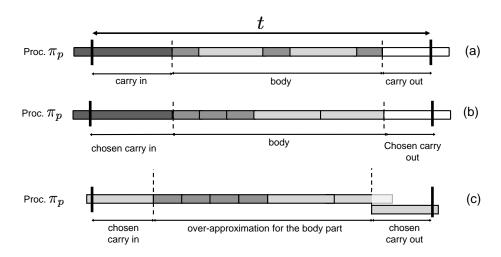

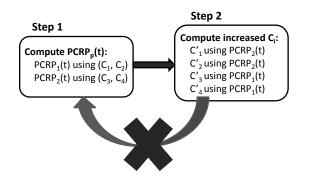

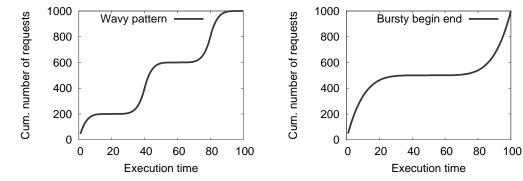

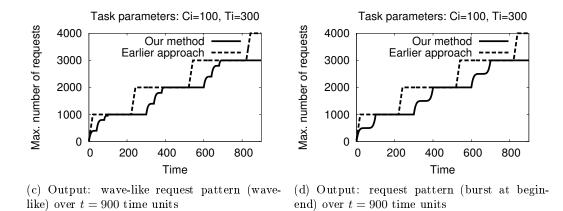

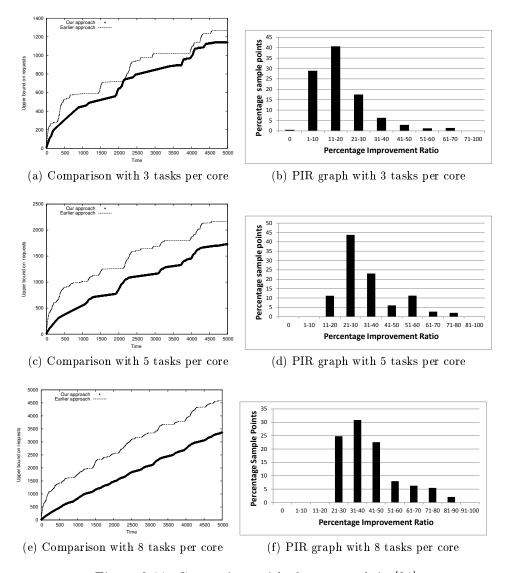

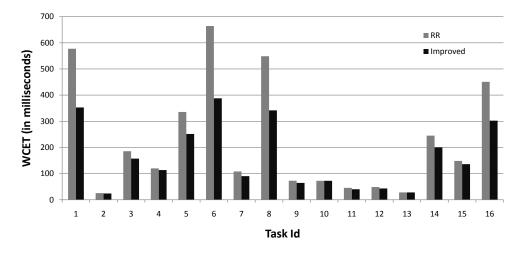

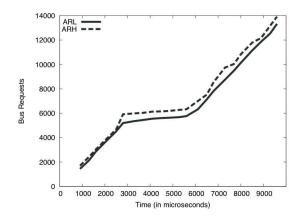

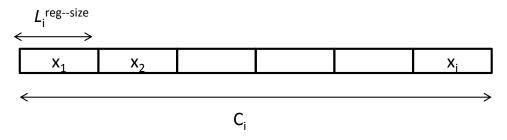

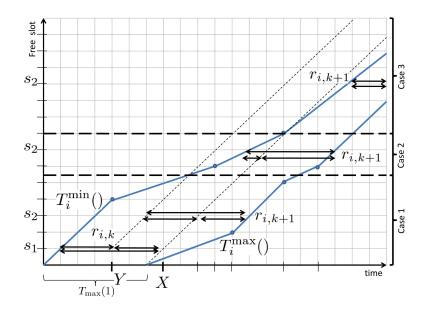

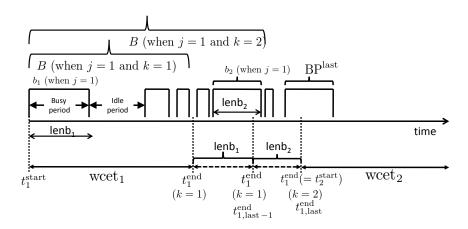

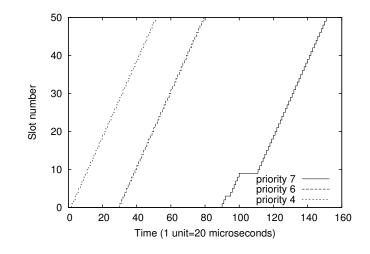

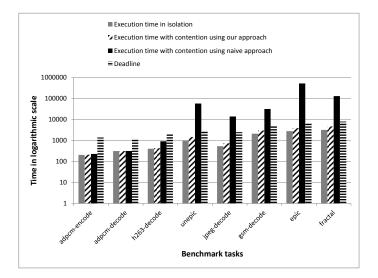

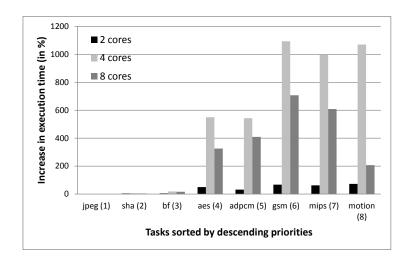

### 1.7 Motivation and Relevance of this work