# PhD Thesis

# Timing Analysis of General-Purpose Graphics Processing Uni ts for Real-Time Systems: Models and Analyses

Kostiantyn Berezovskyi

CISTER-TR-160611

# Timing Analysis of General-Purpose Graphics Processing Uni ts for Real-Time Systems: Models and Analyses

#### Kostiantyn Berezovskyi

**CISTER Research Center**

Polytechnic Institute of Porto (ISEP-IPP)

Rua Dr. António Bernardino de Almeida, 431

4200-072 Porto

Portugal

Tel.: +351.22.8340509, Fax: +351.22.8321159

E-mail:

http://www.cister.isep.ipp.pt

#### Abstract

Graphics processors were originally developed for rendering graphics but have evolved towards being an architecture for general-purpose computations. These processors are well-suited for massively parallel computational problems because of the ability to efficiently manage a great number of lightweight threads competing for the computational resources of the processor. To day, Graphics Processing Units (GPUs) are widely used to unload Central Processing Units (CPUs), liberate other resources of a given computer system, and provide an alternative to multiprocessor computers as a means of processing computationally expensive parallel tasks. The recent trend of utilizing GPUs in embedded systems necessitates developing timing analysis approaches for finding bounds on the execution time of GPU-threads because the approaches developed for CPU timing analysis are not applicable. The reason is that we are not interested in how long it takes for any given GPU thread to complete, but rather how long it takes for all of the GPU threads to complete in the context of their competition for the functional units. We developed both theoretical and practical approaches for GPU timing analysis that could provide exact values and tight upper bounds, marginally optimistic lower bounds or probabilistic upper bounds on the worst-case temporal behavior of GPU processing. We call these approaches optimization-based, metaheuristic-based and statistical measurement-based respectively. We formulate them subject to the hardware features, tractability constraints and some simplifying assumptions. First, we proposed a model of a single streaming multiprocessor - a computationally independent module of a GPU. The optimization-based and metaheuristic-based approaches are formulated in the context of that theoretical model and related assumptions. The measurement-based approach is targeting the real GPU hardware and is ready for practical usage. The optimization-based approach is built up on a simple but very pessimistic technique for finding an upper bound on the worst-case makespan - the longest possible time interval between the moment when the "earliest" GPU thread starts its execution, and the moment when the "latest" thread finishes. The outcome of this technique is used for the formulation of a combinatorial optimization problem for finding an exact value of the worst-case execution requirement. Addressing the issue of tractability, we also proposed a marginally pessimistic estimation technique for finding a tight upper-bound on the worst-case makespan. This approach was implemented in a timing analysis software tool applicable to the problem instance under consideration subject to the configuration of the streaming multiprocessor. Pursuing an objective of discovering computationally fast approaches we addressed the problem of finding the worst-case makespan from the metaheuristic view point. We experimentally demonstrated that the metaheuristic-based approach is able to find a tight lower bound and in combination with the optimization-based approach proposes a complete framework for bounding the respective solution from both. the top and the bottom. This aspect is of paramount importance for the cases when an exact worst-case makespan of the problem under consideration cannot be tractably computed. On the other hand, the simplicity, flexibility and ability for massive parallelization of the metaheuristic-based approach determine a potential of its usage for soft real-time systems. Aiming to bring our research closer to the industry, in order to overcome some limiting assumptions of memory subsystem, we addressed the problem of GPU timing analysis from the probabilistic and measurement-based perspectives. Our statistical measurement-based approach includes a marginally invasive technique for obtaining the GPU execution time measurements. For analyzing these measurements, the approach introduced a probabilistic characterization of the worst-case temporal behavior of GPU applications. We formulated our approach based on a solid statistical background of Extreme Value Theory (EVT) and the "Block Maxima" paradigm. The applicability of EVT was extended to less constraining hypotheses than independence. We also provided a way for obtaining accurate estimates on the worst-case execution requirement for the desired confidence level.

## Timing Analysis of General-Purpose Graphics Processing Units for Real-Time Systems: Models and Analyses

A Dissertation Thesis by

Kostiantyn Berezovskyi

supervised by Dr. Konstantinos Bletsas

Submitted to the graduate faculty of the

Faculdade de Engenharia da Universidade do Porto

Departamento de Engenharia Electrotécnica e de Computadores

in partial fulfillment of the requirements

for the Dissertation Thesis and

subsequent Ph.D. in Electrical and Computer Engineering

© 2015

Kostiantyn Berezovskyi

ALL RIGHTS RESERVED

# Timing Analysis of General-Purpose Graphics Processing Units for Real-Time Systems: Models and Analyses

### Kostiantyn Berezovskyi

Doctoral Program in Electrical and Computer Engineering

### Approved by:

President: Dr. Aurélio Joaquim de Castro Campilho

External Referee: Dr. Shinpei Kato

External Referee: Dr. Christine Rochange

Internal Referee: Dr. Eduardo Manuel de Médicis Tovar

Internal Referee: Dr. José Alfredo Ribeiro da Silva Matos

Internal Referee: Dr. Pedro Alexandre Guimarães Lobo Ferreira Souto

Internal Referee: Dr. João Paulo de Castro Canas Ferreira

Supervisor: Dr. Konstantinos Bletsas

### Acknowledgements

The completion of this thesis was possible because of the supervision, knowledge, help and support from many beautiful people who I was lucky to meet.

Firstly, I would like to thank my supervisor. This dissertation simply would not have been possible without his contributions. Guiding me was an exhaustive workload that required much effort, planning and meetings on daily basis. I am grateful to Konstantinos Bletsas for his insightful ideas, fruitful suggestions, patience and optimism that he was demonstrating especially at those moments when the things were not running well on my side.

The role of my co-authors, without who I would not be able to complete none of those publications, was of paramount importance. I would like to thank Eduardo Tovar, Luca Santinelli, Fabrice Guet, Stefan M. Petters and Björn Andersson for their tireless work and selfless collaboration.

The influence of my professors would be hard to overestimate. I wish to thank Mário Sousa, Luís Almeida, José Fernando Oliveira, Luís Miguel Pinho, Mário Alves, Shashi Prabh, Sónia Amorim, Maria do Carmo Lopes, Jorge Porto, Helena Fernandes, Artur Carvalho and Anatolii Doroshenko for their fun classes and interesting assignments.

Addressing bureaucratic issues turned out to be a demanding task for me. I am grateful to Inês Almeida, Cristiana Barros and Sandra Almeida for their help.

I was lucky to get many useful advices from Pedro Souto, Luis Lino Ferreira, Filipe Pacheco, Michele Albano, Per Lindgren, Vincent Nlis, Geoffrey Nelissen, António Barros, Matthias Becker, Davide Compagnin, Arvind Easwaran and Andrea Baldovin.

Working with hardware was an interesting part of my work. I would like to thank André Ribeiro and Marwin Adorni for giving me a hand on that.

I had a chance to share office space with bright colleagues, who taught me a lot and also created competitive environment. Therefore, I would like to thank Artem Burmyakov, Borislav Nikolic, Hazem Ali, José Marinho, Gurulingesh Raravi, Dakshina Dasari, Vikram Gupta, Suhas Aggarwal, Harrison Kurunathan, Shashank Gaur, André Pedro, Renato Ayres, Paulo Barbosa, Humberto Carvalho, Bruno Deveza, Jose Santos, José Bruno Silva and Muhammad Ali Awan.

My adaptation in Portugal would be much tougher without the help of my friends.

I wish to express my gratitude to José Fonseca, Ricardo Severino, Paulo Baltarejo Sousa, João Loureiro, Alexandre Esper, Cludio Maia, David Pereira, José Augusto Santos and Pedro Santos for helping me to improve my Portuguese skills.

Getting in touch with the local culture was greatly facilitated thanks to the help of Tiago Martins, Krystallenia Batziou and Joana Ilhão.

Living abroad is not an easy experience, thus, I am thankful to Lorenzo Lanzi, Juliane Oliveira and Miguel Lanzi Oliveira for creating for me a family-environment far from home.

I would like to thank all the members of my dear family for their every-day support and for inspiring me with their scientific and engineering achievements.

I wish to thank wonderful Portugal and beautiful Porto for allowing me, the foreigner, to feel myself over here like being at home.

Finally, this work was partially supported by FCT under PhD grant SFRH/BD/82069/2011.

### **Declaration**

Some parts of this thesis proposal have appeared in the previously published paper (the respective author is marked by the asterisk):

- K. Berezovskyi\*, K. Bletsas, and B. Andersson. Makespan computation for GPU threads running on a single streaming multiprocessor. In Proceedings of the 24th Euromicro Conference on Real-Time Systems (ECRTS'2012), July 2012.

- K. Berezovskyi\*, K. Bletsas, and S. M. Petters. Faster makespan estimation for GPU threads on a single streaming multiprocessor. In Proceedings of the 18th IEEE International Conference on Emerging Technologies and Factory Automation (ETFA'2013), September 2013.

- K. Berezovskyi\*, L. Santinelli, K. Bletsas, and E. Tovar. WCET Measurement-based and Extreme Value Theory Characterisation of CUDA Kernels. In Proceedings of the 22nd International Conference on Real-Time Networks and Systems (RTNS 2014), October 2014.

- K. Berezovskyi\*, F. Guet, L. Santinelli, K. Bletsas, and E. Tovar. Measurement-Based Probabilistic Timing Analysis for Graphics Processing Units. Accepted to the 29th International Conference on Architecture of Computing Systems (ARCS 2016).

### Resumo

Originalmente, os GPUs (*Graphics Processing Units*) foram desenvolvidos especificamente para acelerar a renderização gráfica. Hoje em dia, esta tecnologia suporta o processamento das mais diversas operações computacionais, o que faz com que seja amplamente usada de forma a retirar carga ao CPU (*Central Processing Unit*) e libertar outros recursos do sistema. Em particular, os GPUs são adequados para solucionar problemas computacionais massivamente paralelos, uma vez que gerem com eficiência a interação entre uma grande quantidade de *threads* de curta duração e as unidades de processamento.

A utilização de GPUs, em sistemas embebidos, implica o desenvolvimento de análises que permitam calcular os limites no tempo de execução das GPU-threads, já que as análises existentes para CPUs não são aplicáveis. O que é fundamental neste caso, não é saber quanto tempo demora a computação de cada uma das GPU-threads, mas sim quanto tempo demora para que todas concluam a execução, tendo em consideração a competição que se verifica no acesso aos recursos do GPU.

Nesta dissertação, nós desenvolvemos abordagens teóricas e práticas para a análise temporal de tarefas paralelas a serem processadas por GPUs. Mais propriamente, o objectivo é fornecer valores exactos ou limites susperiores próximos do exacto, limites superiores probabilísticos, e limites inferiores marginalmente otimistas, em relação àquilo que é o pior comportamento temporal na sequência de execução das tarefas no GPU. Estas abordagens são designadas optimization-based, probabilistic measurement-based e metaheuristic-based, respectivamente. A sua formulação tem em conta as característica do hardware, restrições de tratabilidade e algumas suposições convenientes.

### Abstract

Graphics processors were originally developed for rendering graphics but have evolved towards being an architecture for general-purpose computations. These processors are well-suited for massively parallel computational problems because of the ability to efficiently manage a great number of lightweight threads competing for the computational resources of the processor. Today, Graphics Processing Units (GPUs) are widely used to unload Central Processing Units (CPUs), liberate other resources of a given computer system, and provide an alternative to multiprocessor computers as a means of processing computationally expensive parallel tasks. The recent trend of utilizing GPUs in embedded systems necessitates developing timing analysis approaches for finding bounds on the execution time of GPU-threads because the approaches developed for CPU timing analysis are not applicable. The reason is that we are not interested in how long it takes for any given GPU thread to complete, but rather how long it takes for all of the GPU threads to complete in the context of their competition for the functional units.

We developed both theoretical and practical approaches for GPU timing analysis that could provide exact values and tight upper bounds, marginally optimistic lower bounds or probabilistic upper bounds on the worst-case temporal behavior of GPU processing. We call these approaches optimization-based, metaheuristic-based and statistical measurement-based respectively. We formulate them subject to the hardware features, tractability constraints and some simplifying assumptions.

First, we proposed a model of a single streaming multiprocessor – a computationally independent module of a GPU. The optimization-based and metaheuristic-based approaches are formulated in the context of that theoretical model and related assumptions. The measurement-based approach is targeting the real GPU hardware and is ready for practical usage.

The optimization-based approach is built upon a simple but very pessimistic tech-

nique for finding an upper bound on the worst-case makespan – the longest possible time interval between the moment when the "earliest" GPU thread starts its execution, and the moment when the "latest" thread finishes. The outcome of this technique is used for the formulation of a combinatorial optimization problem for finding an exact value of the worst-case execution requirement. Addressing the issue of tractability, we also proposed a marginally pessimistic estimation technique for finding a tight upper-bound on the worst-case makespan. This approach was implemented in a timing analysis software tool applicable to the problem instance under consideration subject to the configuration of the streaming multiprocessor.

Pursuing an objective of discovering computationally fast approaches we addressed the problem of finding the worst-case makespan from the metaheuristic viewpoint. We experimentally demonstrated that the metaheuristic-based approach is able to find a tight lower bound and in combination with the optimization-based approach proposes a complete framework for bounding the respective solution from both, the top and the bottom. This aspect is of paramount importance for the cases when an exact worst-case makespan of the problem under consideration cannot be tractably computed. On the other hand, the simplicity, flexibility and ability for massive parallelization of the metaheuristic-based approach determine a potential of its usage for soft real-time systems.

Aiming to bring our research closer to the industry, in order to overcome some limiting assumptions of memory subsystem, we addressed the problem of GPU timing analysis from the probabilistic and measurement-based perspectives. Our statistical measurement-based approach includes a marginally invasive technique for obtaining the GPU execution time measurements. For analyzing these measurements, the approach introduced a probabilistic characterization of the worst-case temporal behavior of GPU applications. We formulated our approach based on a solid statistical background of Extreme Value Theory (EVT) and the "Block Maxima" paradigm. The

applicability of EVT was extended to less constraining hypotheses than independence. We also provided a way for obtaining accurate estimates on the worst-case execution requirement for the desired confidence level.

## Outline

| 1        | Intr                            | oduct                                | ion                                         | 1  |  |  |

|----------|---------------------------------|--------------------------------------|---------------------------------------------|----|--|--|

|          | 1.1                             | 1 Problem Statement                  |                                             |    |  |  |

|          | 1.2                             | Resea                                | rch Approach                                | 2  |  |  |

|          | 1.3                             | Thesis                               | s Statement                                 | 3  |  |  |

|          | 1.4                             | Thesis                               | s Organization                              | 3  |  |  |

| <b>2</b> | Background on computing systems |                                      |                                             |    |  |  |

|          | 2.1                             | Embe                                 | dded and general-purpose computing systems  | 5  |  |  |

|          | 2.2                             | Prince                               | eton and Harvard architectures              | 7  |  |  |

|          | 2.3                             | Circui                               | it organization                             | 10 |  |  |

|          | 2.4                             | Micro                                | architectures                               | 12 |  |  |

|          | 2.5                             | Graph                                | nics Processing Unit                        | 14 |  |  |

|          | 2.6                             | Opera                                | ational cycle                               | 15 |  |  |

| 3        | Literature Review 1             |                                      |                                             |    |  |  |

|          | 3.1                             | Introduction to real-time systems    |                                             |    |  |  |

|          | 3.2                             | Rate-Based Execution model           |                                             |    |  |  |

|          | 3.3                             | 3 Parallel task models               |                                             |    |  |  |

|          |                                 | 3.3.1                                | Gang model                                  | 27 |  |  |

|          |                                 | 3.3.2                                | Independent thread models                   | 31 |  |  |

|          | 3.4 Graph-based models          |                                      |                                             |    |  |  |

|          |                                 | 3.4.1                                | Processing Graph Method                     | 37 |  |  |

|          |                                 | 3.4.2                                | Directed Acyclic Graph (DAG) model          | 39 |  |  |

|          | 3.5                             | 5 Worst-case execution time analysis |                                             |    |  |  |

|          |                                 | 3.5.1                                | Sources of performance and unpredictability | 48 |  |  |

|          |                                 | 3.5.2                                | Static methods                              | 52 |  |  |

|          |                                 | 3.5.3                                | Measurement-based methods                   | 53 |  |  |

|   | 3.6 | 3.6 Probabilistic real-time systems |                                                             |            |  |  |  |

|---|-----|-------------------------------------|-------------------------------------------------------------|------------|--|--|--|

|   |     | 3.6.1                               | Probabilistic response time analysis                        | <u>,</u>   |  |  |  |

|   |     | 3.6.2                               | Probabilistic timing analysis                               | įĆ         |  |  |  |

|   |     |                                     | 3.6.2.1 Static Probabilistic Timing Analysis 6              | j(         |  |  |  |

|   |     |                                     | 3.6.2.2 Measurement-Based Probabilistic Timing Analysis . 6 | ;7         |  |  |  |

|   | 3.7 | Timin                               | g analysis of architectures with co-processors              | <b>'</b> 4 |  |  |  |

|   |     | 3.7.1                               | Suspension-oblivious approach                               | 'E         |  |  |  |

|   |     | 3.7.2                               | Suspension-aware approaches                                 | ' [        |  |  |  |

|   | 3.8 | GPU :                               | performance analysis for the average case                   | 7          |  |  |  |

|   | 3.9 | GPUs                                | in real-time research                                       | '8         |  |  |  |

|   |     | 3.9.1                               | GPU resource management                                     | <b>'</b> C |  |  |  |

|   |     | 3.9.2                               | GPU data transfer                                           | 30         |  |  |  |

|   |     | 3.9.3                               | GPUs in cyber-physical systems                              | )2         |  |  |  |

|   |     | 3.9.4                               | GPU timing analysis                                         | );         |  |  |  |

| 4 | GP  | U mod                               | lel 8                                                       | 7          |  |  |  |

|   | 4.1 | GPU :                               | programming model                                           | 37         |  |  |  |

|   | 4.2 | GPU                                 | architecture model                                          | )(         |  |  |  |

|   |     | 4.2.1                               | Streaming multiprocessor                                    | )]         |  |  |  |

|   |     | 4.2.2                               | Entities of computation                                     | 12         |  |  |  |

|   |     | 4.2.3                               | Simplifying assumptions                                     | 3(         |  |  |  |

|   |     | 4.2.4                               | Kernel instruction string                                   | )4         |  |  |  |

|   |     | 4.2.5                               | Architectural details                                       | 16         |  |  |  |

|   | 4.3 | Summ                                | ary                                                         | 3(         |  |  |  |

| 5 | Opt | imizat                              | ion-based approach 10                                       | 1          |  |  |  |

|   | 5.1 | Pessin                              | nistic makespan derivation                                  | )]         |  |  |  |

|   | 5.2 | ILP d                               | erivation                                                   | ):         |  |  |  |

|   |      | 5.2.1 Objective function                        |

|---|------|-------------------------------------------------|

|   |      | 5.2.2 Capacity constraints                      |

|   |      | 5.2.3 Precedence constraints                    |

|   |      | 5.2.4 Work-conserving constraints               |

|   | 5.3  | Alternative optimization problem formulation    |

|   | 5.4  | Summary of the ILP formulation                  |

|   | 5.5  | Resolving the issue of tractability             |

|   | 5.6  | Experiments                                     |

|   | 5.7  | Summary                                         |

| 6 | Met  | aheuristic-based approach 141                   |

|   | 6.1  | Warp pseudo-precedence string                   |

|   | 6.2  | The metaheuristic                               |

|   | 6.3  | Providing a suitable initial solution           |

|   |      | 6.3.1 "Round-robin"                             |

|   |      | 6.3.2 "Fixed-priority"                          |

|   |      | 6.3.3 Most Pending Warp Executes First          |

|   | 6.4  | Implementation optimization                     |

|   | 6.5  | Case studies                                    |

|   |      | 6.5.1 Overview                                  |

|   |      | 6.5.2 The benchmark                             |

|   |      | 6.5.3 Experimental results                      |

|   | 6.6  | Summary                                         |

| 7 | Stat | istical measurement-based approach 159          |

|   | 7.1  | On Collecting Measurements                      |

|   | 7.2  | Statistical Analyses of Execution Time          |

|   |      | 7.2.1 On the Verification of the EVT hypotheses |

|                           |       |        | 7.2.1.1     | Independence of Observations           | 168 |

|---------------------------|-------|--------|-------------|----------------------------------------|-----|

|                           |       |        | 7.2.1.2     | Identical Distribution of Observations | 168 |

|                           |       | 7.2.2  | Statistic   | al Analyses                            | 168 |

|                           | 7.3   | Experi | iments .    |                                        | 170 |

|                           |       | 7.3.1  | Timing .    | Analysis                               | 171 |

|                           |       | 7.3.2  | From the    | e Measurements to the pWCET            | 173 |

|                           | 7.4   | Summ   | ary         |                                        | 180 |

| 8                         | Con   | clusio | n           |                                        | 183 |

|                           | 8.1   | On the | e optimiza  | ation-based approach                   | 183 |

|                           | 8.2   | On the | e metaheı   | ıristic-based approach                 | 184 |

|                           | 8.3   | On the | e statistic | al measurement-based approach          | 185 |

|                           | 8.4   | Closin | g remarks   | S                                      | 186 |

| $\mathbf{A}_{\mathbf{l}}$ | ppen  | dix    |             |                                        | 187 |

|                           | The   | orem 4 |             |                                        | 188 |

|                           | The   | orem 5 |             |                                        | 190 |

|                           | The   | orem 6 |             |                                        | 200 |

| Bi                        | bliog | graphy |             |                                        | 201 |

# List of Figures

| 1  | Basic scheme of the Princeton hardware achitecture                                             | (   |

|----|------------------------------------------------------------------------------------------------|-----|

| 2  | Basic scheme of the Harvard hardware achitecture                                               | 9   |

| 3  | A simplified scheme of the NVIDIA Kepler GPU chip                                              | 14  |

| 4  | A simplified scheme of an operational cycle                                                    | 16  |

| 5  | A simplified scheme of the NVIDIA Kepler GK104 GPU chip that                                   |     |

|    | contains 8 streaming multiprocessors                                                           | 91  |

| 6  | Possible schedule (round-robin, $\sigma_L = \sigma_C = 1$ ) as a valid solution                | 96  |

| 7  | Transformation of the kernel instruction string                                                | 98  |

| 8  | Possible schedule $(\sigma_L = \sigma_C = 1)$                                                  | 102 |

| 9  | The complete ILP formulation (using short constraints)                                         | 116 |

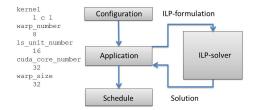

| 10 | Typical configuration file and application workflow                                            | 138 |

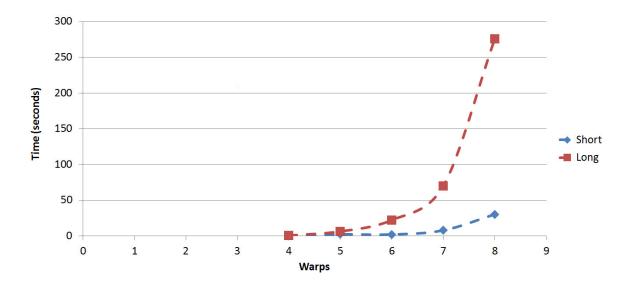

| 11 | Computation time for solving ILP-problem with short and long con-                              |     |

|    | straints ( $\sigma_L = \sigma_C = 1$ , "LLCLL")                                                | 138 |

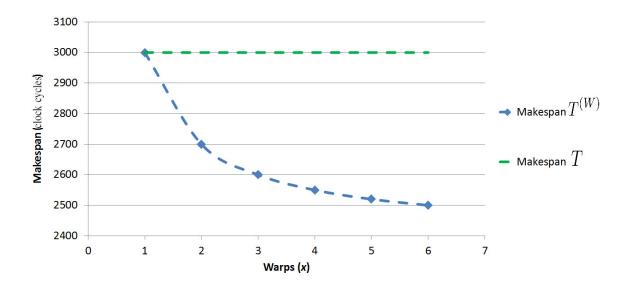

| 12 | Convergence of $T^{(W)}$ with increasing $x$ ( $W$ =600, $\sigma_L$ = $\sigma_C$ =1, "LLCLL"). |     |

|    | The horizontal dashed line corresponds to the pessimistic estimate                             |     |

|    | T (Section 5.1)                                                                                | 139 |

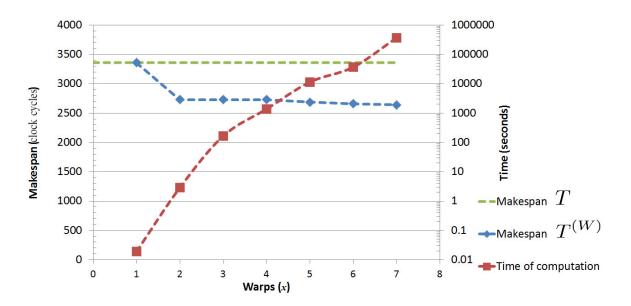

| 13 | Growth of computation time and convergence of $T^{(W,x)}$ with increasing                      |     |

|    | $x \ (W = 420,  \sigma_L = \frac{1}{2},  \sigma_C = 1,  \text{"LCLCL"})$                       | 140 |

| 14 | Possible schedule ( $\sigma_L = \sigma_C = 1$ ) as a valid solution                            | 142 |

| 15 | An invalid solution (the work-conserving property is violated) $\dots$                         | 142 |

| 16 | The algorithm for constructing the schedule                                                    | 144 |

| 17 | A valid neighbour solution (with increased makespan)                                           | 144 |

| 18 | Fixed-priority $(\sigma_L = \sigma_C = 1)$                                                     | 148 |

| 19 | Most Pending Warp Executes First $(\sigma_L = \sigma_C = 1)$                                   | 148 |

| 20 | Constructing a "Most Pending Warp Executes First" initial solution.                            | 150 |

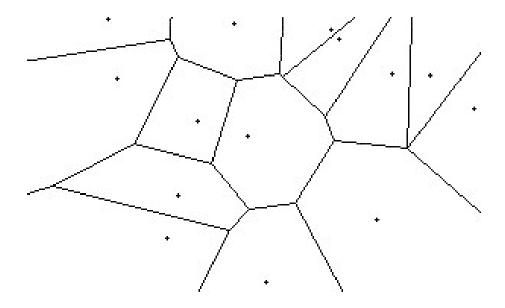

| 21 | Voronoi diagram for a set S of limit points                                                    | 153 |

| 22 | Simple Voronoi diagram representing code                                    | 154 |

|----|-----------------------------------------------------------------------------|-----|

| 23 | PTX program for visualizing Voronoi diagrams                                | 155 |

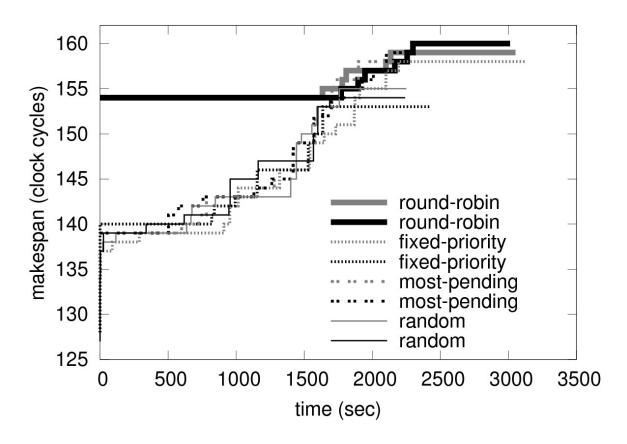

| 24 | Convergence of the estimates of the worst-case makespan over time,          |     |

|    | for 8 instances of the metaheuristic, with different initial solutions      | 157 |

| 25 | High-level overview of the measurement-collecting assembly inserted in      |     |

|    | each GPU thread                                                             | 162 |

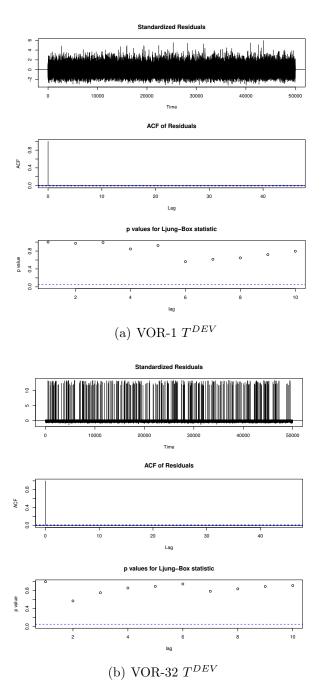

| 26 | Statistics from the autocorrelation function (ACF) and the Ljung-Box        |     |

|    | statistics. VOR-1 and VOR-32 $T^{DEV}$ compared                             | 174 |

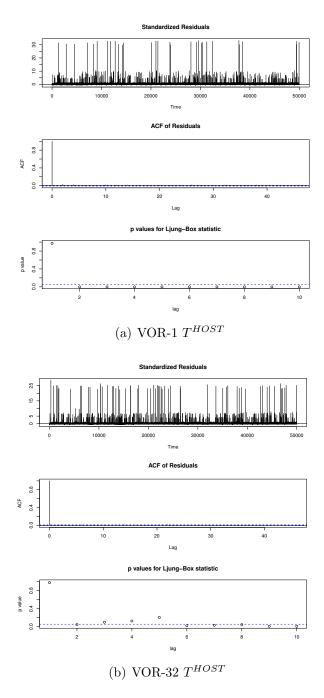

| 27 | Statistics from the autocorrelation function (ACF) and the Ljung-Box        |     |

|    | statistics. VOR-1 and VOR-32 $T^{HOST}$ compared                            | 175 |

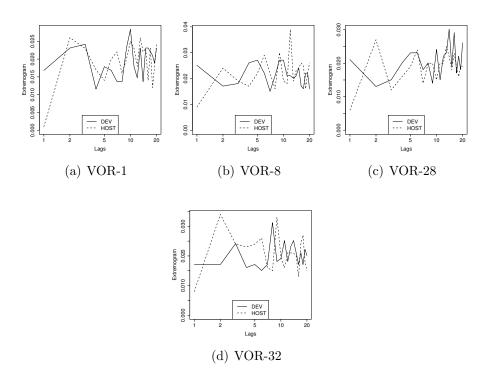

| 28 | Measurement extremogram up to 20 observations lag. $T^{DEV}$ and $T^{HOST}$ |     |

|    | compared                                                                    | 176 |

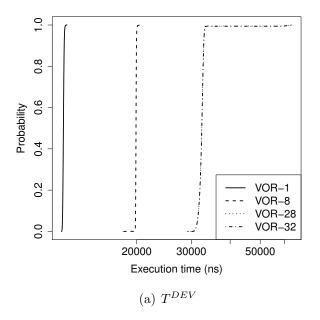

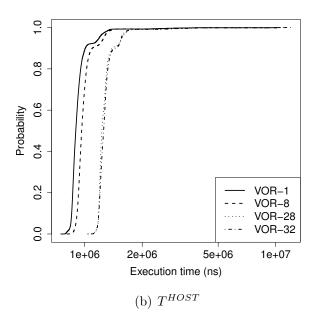

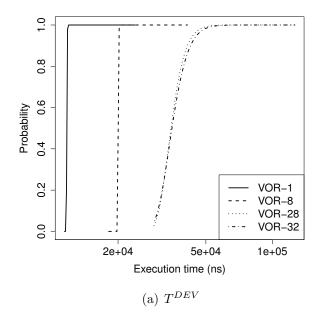

| 29 | Measurements for all the VORONOI cases. CDF representation of the           |     |

|    | distributions                                                               | 177 |

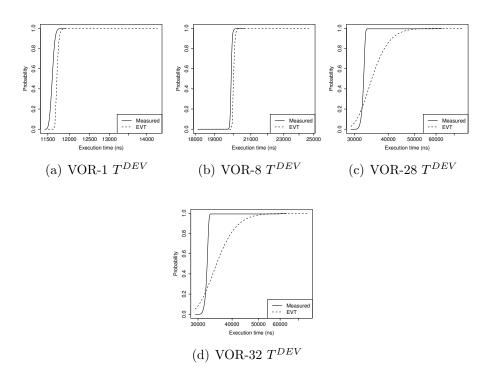

| 30 | EVT applied to VOR-1, VOR-8, VOR-28 and VOR-32 $T^{DEV}.$ Com-              |     |

|    | parison of measurements vs EVT, CDF representations                         | 178 |

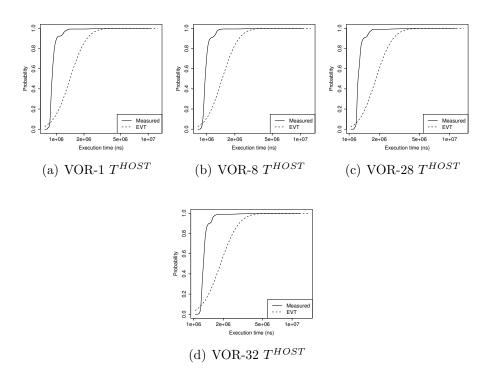

| 31 | EVT applied to VOR-1, VOR-8, VOR-28 and VOR-32 $T^{HOST}.$ Com-             |     |

|    | parison of measurements vs EVT, CDF representations                         | 179 |

| 32 | CDF EVT distributions for $T^{DEV}$ , $T^{HOST}$                            | 181 |

| 33 | Determining the value of Z in Case 2.0                                      | 195 |

| 34 | Determining the value of Z in Case 2.1                                      | 197 |

## List of Tables

| 1 | Independence, stationarity and extremal tests                                               | 173 |

|---|---------------------------------------------------------------------------------------------|-----|

| 2 | EVT estimates for $T^{DEV}$ and $T^{HOST}$ at $10^{-6}$ , $10^{-9}$ , and $10^{-12}$ proba- |     |

|   | bility thresholds.                                                                          | 180 |

### 1 Introduction

The massive computational power of Graphics Processing Units (GPUs), combined with novel programming models such as CUDA [156], makes them attractive platforms for many parallel applications. For example, for signal processing applications, a GPU is a good choice for a platform due to their availability and highly developed software ecosystem. This also includes embedded and real-time applications, which, however, also have temporal constraints: computations must not only be correct but also completed on time. This poses a challenge because the characterization of the worst-case temporal behavior of parallel applications on GPUs is still an open problem.

#### 1.1 Problem Statement

To provide temporal guarantees for GPU-accelerated applications, we need approaches for upper-bounding their execution time on the GPU. Traditional Worst-Case Execution Time (WCET) [182] analyses for Central Processing Units (CPUs) are inapplicable because they focus on the WCET of a single entity of execution (i.e., a thread). Yet, on GPUs the result is pieced together from thousands of threads, competing for GPU resources, and we are not interested in the WCET of any single thread in particular. Rather, we seek to bound the time, from when the earliest GPU thread starts executing until all of them have completed. On the other hand, the evidence shows that the timing analysis techniques developed for CPUs cannot even be considered as applicable to graphics processors because of the crucial differences of CPU and GPU architectures. The need for GPU timing analysis, that real-time embedded system community faces these days, is reflected in the novel research topic of this dissertation: "Timing Analysis of General Purpose Graphics Processor Units for Real-Time Systems".

### 1.2 Research Approach

Given that today's GPU architectures are subject to substantial changes in between revisions to the hardware, many of their important features (e.g., internal scheduling policy) are left undocumented. This gives to the chip-makers the freedom of taking different technological paths and making experimental designs, but on the other hand it poses a challenge for the researchers and engineers who make timing analysis for these hardware architectures and target meeting the timing requirements of the real-time systems powered by the GPUs. Our way of addressing this problem could be briefly described via the following two research directions:

- developing static approaches for finding upper and lower bounds on the kernel execution time;

- formulating and validating a Measurement-Based Probabilistic Timing Analysis approach (MBPTA) based on Extreme Value Theory (EVT).

The process of developing static approaches is subject to the following high-level steps:

- creating models of the GPU hardware by giving the preference to pessimistic rather than optimistic assumptions;

- developing and implementing the techniques for obtaining the bounds on the worst-case execution timings of GPU kernels subject to the models under consideration.

Unlike the approaches mentioned above, probabilistic measurement-based approaches target directly the hardware, rather than its models. A worst-case execution requirement estimate, provided by an approach of such kind, is subject to a probability that the respective estimate will not be exceeded. These approaches are based on the following two stages:

- creating techniques for profiling GPU kernel execution on real hardware with the least possible measurement overhead and collecting the corresponding timings;

- applying Extreme Value Theory (EVT) to the measurements collected during the previous stage for the sake of providing an accurate probabilistic worst-case estimate.

#### 1.3 Thesis Statement

Elliott demonstrated [56] that the use of GPUs is beneficial for real-time systems and such an integration is expected to be effective in real-life scenarios. We use the statement of his dissertation as a basis for our motivation, which allows us to concentrate on addressing a timing analysis problem which is required for a successful application of GPUs in the real-time domain. Therefore, the statement of this thesis is the following:

The problem of GPU timing analysis can be successfully addressed in the context of real-time systems. The resulting approaches represent the range of modern timing analysis research: from static to measurementbased, subject to the strictness of timeliness guarantees of the respective real-time application. These techniques have a potential to satisfy the future industrial needs.

### 1.4 Thesis Organization

The remainder of this thesis is organized as follows: Chapter 2 introduces computing systems. Chapter 3 presents the literature review. Chapter 4 introduces the model of GPU chip architecture and the GPU programming model. Chapter 5 discusses an approach based on optimization problems. Chapter 6 introduces a metaheuristic-based approach. Chapter 7 presents a probabilistic approach based on measurements,

Chapter 8 discusses future work directions and concludes.

### 2 Background on computing systems

Let us consider a *signal* as a transmitted energy from which some information can be obtained. An *information* is that which *informs* and from which *data* can be derived. Data refers to some information that is *coded* or represented in some form being amenable for *processing* or usage. An *information processing system* is a system which takes information in one form and processes it into another form by deriving data and organizing it according to some *logic*. In this thesis we consider a *computing system* to be an electrical information processing system organized as a combination of two subsystems: *hardware* and *software*.

Hardware is the collection of physical components. It includes both, essential components that are necessary for the computing system to function, and auxiliary components that provide additional functionalities. All these components process instructions, where each instruction is an atomic operation supported by the hardware (subject to the respective functional requirements implemented).

Sequences of instructions, grouped together according to some logic, form software. It is the software that specifies the workload to be performed by the hardware. Therefore, hardware and software have to work together for the sake of forming a usable computing system.

Among computing systems there is a distinction between two broad categories: embedded systems and general-purpose systems.

### 2.1 Embedded and general-purpose computing systems

An embedded system is designed to be a subsystem of a more complex system that includes other electrical parts, mechanical parts, etc. Therefore, such a computing system is *embedded* as part of larger *host system*<sup>1</sup> [181]. Usually, embedded systems

$<sup>^{1}</sup>$ In this thesis, we use the term *host system* for a bigger system that includes the embedded system under consideration. Note, that this is a different meaning comparing to *end system* from

are characterized by a fixed set of dedicated tasks to be performed. In this sense, an embedded system is custom-made for a specific application domain subject to concerns regarding functional and non-functional requirements of the host system.

The concept of an embedded system is tightly related to the concept of a controller – a device that monitors and controls the operation of a given dynamical system, e.g., maintaining settings for liquid flow, temperature, pressure, etc. Historically, controllers were implemented by combining mechanical, pneumatic and hydraulic components. However, rapid development in electronic science and technology has brought a huge variety of electronic controllers. Although the term controller can be used to refer to a stand-alone controlling device, more often a controller is implemented as an electronic circuit assembled of electronic components connected by wires or traces that provide conductivity for electric current flows. In this case, the controller is in the "heart" of the embedded system, managing and interfacing with other its parts.

A general-purpose computing system, as opposed to an embedded one, is designed to be stand-alone. It has to be configurable and suitable for a broad range of work-loads. The hardware of such systems has potential for augmented functionality while the software often needs to be frequently updated or even replaced. Unlike embedded systems, general-purpose systems do not usually have so strict requirements on power consumption, size and price per unit. Usually, they are not expected to be used in harsh operational conditions, therefore, in the average case, the level of reliability of a general-purpose system can be significantly lower. Because of all such aspects, designers of general-purpose systems often have more freedom in trying new approaches and experimenting with altering configurations. This is the reason of a rapid progress in general-purpose hardware and software which also leads to migration of many general-purpose features to embedded systems domain.

the networking domain of computer engineering, that is sometimes referred to as host system in networking jargon.

The "heart" of general-purpose hardware is the *processor* – a component able to carry out a set of supported arithmetic, logical or control operations. Unlike a controller in embedded systems, a processor has to be suitable for a much broader range of operations, hence, its design is often more complex.

Both embedded and general-purpose computing systems development is greatly influence by two competing hardware architectures: *Princeton* design and *Harvard* design.

#### 2.2 Princeton and Harvard architectures

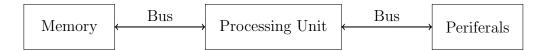

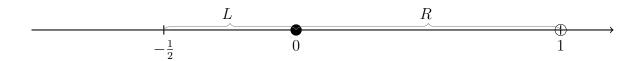

The Princeton hardware architecture [54] also known as the von Neumann computer [178] was dominant in the early years of computer engineering. The basic scheme of that architecture is presented in Figure 1. It consists of: a processing unit, memory, peripherals and buses.

Figure 1: Basic scheme of the Princeton hardware achitecture.

A processing unit is dedicated to executing instructions – operations that given an input and produce an output (that could also be an input to another instruction later on). A sequence of instructions that are grouped logically, for the sake of performing some more or less distinct piece of work, form a *program*, which is a single element of the whole software of the computing system. Potentially, the same program could have alternative representations, e.g., being in a form understandable by machine (machine code) or being represented in a form that is more suitable for humans (high-level abstraction code), expressed with the help of a programming language.

The memory is usually represented as an array of cells each of which is able to store one of two possible states. These binary alternatives could be represented by

"0" and "1", or by any other way to be distinguished, and form a binary digit (bit), of information. All the bits in memory are logically grouped into words of some fixed length, that is dependent on the implementation of the hardware architecture. Each word has a unique address, for the purpose of being accessed by the processing unit.

While the memory/processing unit combination is pivotal for a computing system to function, the peripherals provide auxiliary means that make a computer system useful for interfacing with the outside world. Therefore, thanks to the peripherals, a computer system is not a "thing-in-itself", but a tool for solving real-life problems. The peripherals could be classified as *storage*, *input output* components.

Whilst the memory stores the data during an operation phase, the storage components should be able to hold the data that were successfully processed by the computing system even after it will be turned off. Through the input/output components, a computing system receives/sends signals or data from/to the outside world.

All the hardware components mentioned above are connected by the *bus* wiring – communication pathways that provide signal and data transfers.

The processing unit in the Princeton architecture introduced a generic design that is highly influential in computer engineering. Being a general-purpose circuitry, a processing unit needs to be able to interpret properly the data on which the particular instruction operates. Such information should be specified by the instruction itself, therefore, the Princeton architecture implies distinct subsets of instructions for every type of data e.g., one instruction type for discrete mathematical objects (integers) and another one for continuous mathematical objects (floats). This example of having both integer and floating-point arithmetic implemented in the hardware, makes the processing unit circuitry more complex. As a result, the memory and the peripherals were not incorporated into the same circuit with the processing unit.

One of the key aspects of the Princeton design is the memory model. Any memory location is uniquely identifiable and accessible via its address. Additionally, each

memory location may hold instructions, data of arbitrary types or even addresses of other memory locations. It is up to the software running on the processing unit to keep track of/interpret appropriately the contents of each memory location accessed by it. On the other hand, in program representations the addresses potentially can be manipulated using the instructions designed for data processing. Both features described above, not only provide the flexibility in creating complex dynamically changing data structures, but also open a way for a program potentially misbehaving and unauthorized memory accesses. This requires attention in software and hardware design.

However, in Princeton architecture, where there are no separate memories for instructions and data, the bus input/output for instructions and the bus input/output for data intefere with each other. This may be detrimental for performance in scenarios where the processor has to perform a small amount of work on each element of a huge data. This effect (known as the *von Neumann bottleneck* [8]) does not exist in Harvard architecture [180] where the memories and buses for instructions and data are separate.

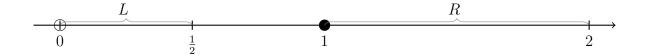

The Harvard memory model is represented as a combination of an *Instruction memory* and a *Data memory* (see Figure 2).

Figure 2: Basic scheme of the Harvard hardware achitecture.

These two memories are independent and do not have to share characteristics, e.g., the implementation technology, the memory address structure, the width of the word, etc. For example, if it is known that the kind of target application requires lots of processing over small data arrays, a system designer would introduce a larger instruction memory and a smaller data memory – therefore, it might be reasonable to make instruction addresses wider compared to data addresses. A strict distinction between the instruction address space and the data address space requires the data embedded in the code (e.g., the constant values) to be copied to the data memory, which is an obvious performance drawback. On the other hand, the separation between these two memories greatly reduces the potential security hazards for the stored instructions in terms of an inappropriate access.

Such a heterogeneous memory model allows to tweak the hardware for a particular application domain, hence, the Harvard architecture gained a strong popularity for the embedded systems implementations. Even though having a less generic memory model, the Harvard design has some strengths that are important also from a general-purpose viewpoint. Given that the instruction traffic and the data traffic do not have to share the same pathway, an instruction read and a data access can be performed in parallel. Thus, due to the absence of the von Neumann bottleneck, a computing system based on the Harvard architecture can potentially be faster compared to a Princeton-based system for a given circuit complexity.

Let us consider the circuit design principles in more detail.

### 2.3 Circuit organization

An electronic circuit can be categorized as being analog, digital or analog-digital.

An analog circuit is an electronic circuit that deals with continuously changing analog signals. This type of signals corresponds to continuous aspects of classical physics phenomena observed in the nature, e.g., electromagnetic field that is considered to extend continuously throughout space. A continuous variability of signal values is proportional to the change in electrical current or voltage that represents

the corresponding signal [2].

Digital signals originate from discretization of analog signals – a simplification made by splitting the range of the analog signal in bounded intervals and abstracting away from every part of the signal by representing it just by a single value from the corresponding part. Such a discretization of an analog signal range allows, to some extent, tolerate noise, interference with other signals, etc., and was utilized in digital circuits. Since, in many cases, it turned to be more reliable to work with digital signals, digital circuits gained a tremendous popularity. Particularly, an approach of dealing with just two valid voltage areas – the lowest possible (marked as "0") and the highest possible (marked as "1"), is widely accepted by the electronic industry which rely on Boolean logic [86].

Typically, most of the electronic components inside a digital circuit, are spent to form the *logic gates*. In a logic gate, the components are arranged in a way to implement some specific boolean function that for a number of binary inputs produces a single binary output. In the voltage range the area between the two extreme areas "0" and "1" is called "forbidden", thus, the corresponding signals are considered to be invalid. The forbidden zone is used to avoid confusing "0" with "1" in a realistic operating conditions where every signal experiences a noise. To tolerate its harmful influence, the voltage bounds for the output signals are more strict when compared to input signals. This is done to anticipate the room for noise by accepting marginally valid input signals, but provide output signals with solid validity.

The analog-digital circuits combine analog and digital approaches. They are very popular for signal amplification, signal conversion from analog form to digital form and vice versa.

The parts of digital circuits can be synchronized or they can work asynchronously.

A synchronous circuit has a notion of time by including a part that generates a clock signal for coordinating all the actions performed by the circuit. This implemen-

tation of the notion of time is based on the propagation delay of the circuit – the time interval between the moment when the input of the logic gate gets stable, and the moment when the output of that gate becomes stable.

Asynchronous circuits do not have central clock. To coordinate the correct sequence of actions they utilize special signals which indicate that the corresponding action was completed. Such an approach of circuit design not only liberates the performance from the bound imposed by the worst-case scenario, but may also bring power efficiency and allow adaptability to operation conditions (e.g., adaptation of the performance subject to temperature change). Although asynchronous circuits are an active topic of research and development, commercial-off-the-shelf circuits are mostly synchronous so far.

From now on in this thesis, by mentioning a circuit, we assume it to be digital and synchronous if the opposite is not explicitly stated.

#### 2.4 Microarchitectures

In the early days of computing systems, electronic circuits were built of independent electronic components. Therefore, such discrete circuits were characterized by huge size, wasteful energy consumption and high direct materials cost. Later, theoretical and practical advancements in semiconductor electronics made it possible to integrate numerous electronic components into a single circuit placed on a small plate ("chip") of semiconductor material. Such integrated circuits, called chips, have replaced discrete circuits in many fields of electrical and computer engineering due to the rapid growth of functional characteristics, lower cost and lower power consumption. Integrated circuits gained tremendous performance boost and popularity to both embedded and general-purpose computing systems bringing front-edge technology advancements to tiny microcontrollers and microprocessors.

Although having revolutionized the world of electronics, semiconductor compo-

nents did not change immediately the high-level principles of general-purpose systems. In microprocessors the main memory remained to be placed on separate chips.

However, in the case of embedded-systems hardware, integrated circuits allowed to take an opposite approach. In microcontrollers the processor, the memory and the peripherals are all placed on a single semiconductor plate. This design principle is very suitable for those embedded systems that had minimal requirements for program length and memory size, since there is no need to implement high-end integrated circuits. Also, this allows to make microcontrollers being attractive by cost and energy consumption.

Although taking a lion's share of processing units market for embedded systems [36], microcontrollers were not able to provide enough performance for the systems (e.g., smartphone hardware) that emerged on the frontier between general-purpose and embedded domains. Such systems require a decent computational power while being able to fit into a relatively small energy budget and pocket-size form-factor. Such requirements motivated a technical direction of implementing a higher system integration in so-called system in package, package on package and system on chip.

System in package includes a number of chips assembled into a single chip carrier ("package"). In package on package, chips are stacked vertically during board assembly. System on chip (SoC) integrates in a single chip a number of components, that were traditionally implemented in stand-alone integrated circuits. However, some parts of such systems are still placed off-chip, e.g., the main memory.

Another possible example of merging of general-purpose and embedded domains could be a Graphics Processing Unit (GPU) – originally an input/output component designed for rendering graphics, that has recently evolved towards being an architecture for general-purpose computations.

## 2.5 Graphics Processing Unit

The term "Graphics Processing Unit" (GPU) was coined [157] by NVIDIA, and naturally, in this thesis we target GPUs designed by this chip-maker. However, the proposed timing analysis approaches can be applied to graphics processors from other vendors as well.

Novel parallel programming models developed for the GPUs brought us to the General-Purpose GPU (GPGPU) [76] computing: the use of GPUs as accelerators for computationally intensive (non-graphics) workloads. The GPUs are widely used to unload the traditional Central Processing Units (CPUs), liberate other resources of a given computing system, and provide an alternative to multiprocessor computers for processing computationally heavy parallel tasks.

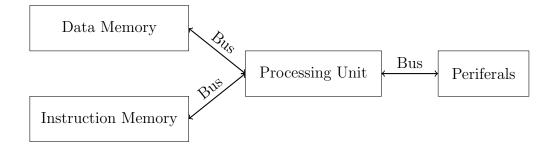

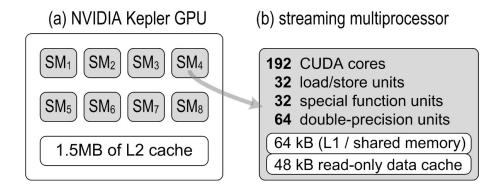

Modern GPUs are immensely parallel architectures. NVIDIA GPU (Figure 3) contains several "Streaming Multiprocessors" (SMs).

Figure 3: A simplified scheme of the NVIDIA Kepler GPU chip.

Each streaming multiprocessor is a complex manycore in itself, as it includes many

- CUDA cores, for integer and floating-point arithmetic;

- "load/store" units that load data from/store data to the memory subsystem;

- special function units, implementing sine, cosine, square root etc., in hardware;

- double precision (64-bit) units.

The big number of cores is determined by the fact that the GPUs leverage an important aspect of typical graphics workload: data in huge arrays does not have dependency, and therefore, can be processed in parallel. Such *data-parallel* workloads are processed by the GPUs achieving high performance not due to the low processing latency of every single core, but due to the high throughput provided by the whole chip. In this sense the microarchitectures discussed earlier in this chapter can be considered as *latency-oriented* processors while the GPUs are *throughput-oriented*.

Nevertheless, despite the substantial differences in their architectures, computing systems based on any of the microarchitectures discussed in this chapter have a similar operational cycle.

## 2.6 Operational cycle

Considering program processing at a high abstraction level, a computing system operates in the following way: the code of the program, that contains a series of logical, arithmetic, control, input/output instructions and associated data, is loaded into the memory and the processor performs each instruction in turn. Although most of the software these days is written in high-level programming languages, eventually, all these high-level codes are translated to machine codes – low-level representations of the instructions encoded in binary form processable by computing system circuitry.

Upon receiving the machine code of the instruction, the processor has to recognize from it what kind of actions that instruction requires from its pre-determined functionality to be able to carry out these actions. All the instructions that are supported by the processor form an *instruction set*, which is often processor/architecture-specific. Each instruction in the instruction set has a unique code, that serves as an

identifier of the instruction and is an obligatory component of any machine code. Together with the *instruction identifier field* (also known as the "opcode"), the machine code holds an *instruction operands field* that specifies where the data read/written by the instruction are stored and how this data could be accessed (an *addressing mode*).

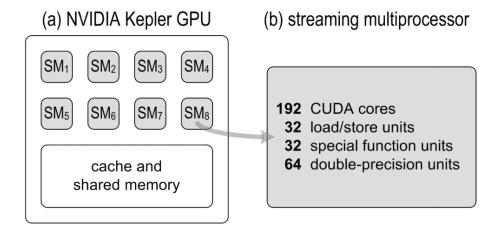

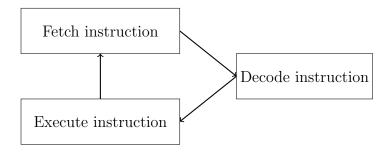

The instructions are processed in an *instruction cycle* – an operational cycle that is continuously repeated from boot-up until shut down of the computing system. Simply speaking, the instruction cycle consists of three phases (see in Figure 4): *fetch*, *decode* and *execute*.

Figure 4: A simplified scheme of an operational cycle.

During the fetch phase, the corresponding machine code is retrieved from the memory and stored in an *instruction register* of the processor – a temporary storage for the instruction to be executed soon. Additionally, other registers of the processor are updated, e.g., the one (also known as *program counter*) that stores the memory address of the instruction to be executed next.

The decode phase stands for the interpretation of the machine code stored inside the instruction register. This is done by examining the instruction identifier field of the machine code for the sake of matching the corresponding instruction from the instruction set of the processor which would allow it to "understand" what kind of actions should be performed to execute that instruction. Then, the instruction operands field should be analyzed in order to get what is the data to process and where it is stored. During the execute phase, the actual function of the instruction is performed. The decoded instruction is passed as a sequence of control signals to the relevant functional units of the processor. Here, for the sake of simplification, we assume that the execute phase includes accessing the data required for the execution and storing the result of the instruction to the memory – also known as "memory access" and "write back" respectively.

Further, we rely on the essencial terminology and the conventions introduced in this chapter to present the review of the literature in the context of the topic of this thesis.

# 3 Literature Review

The current state-of-the-art offers a few methods for GPU timing analysis, however, the research literature offers several results for solving related problems. This chapter serves as a brief review of those works.

## 3.1 Introduction to real-time systems

Real-time computing is usually defined as a study of hardware and software aspects of systems that have time constraints (e.g., a computer that controls an autonomous driving vehicle). In this work we pay attention to software programs that must execute and give response during a particular time window. On the other hand, a non-real-time system is one that has no deadline, even if fast response or good performance is appreciated.

A number of definitions of real-time systems cover a broad spectrum of computing systems. A definition of Randell et al. [166] is the following: "A real-time system is a system that is required to react to stimuli from the environment (including the passage of physical time) within time intervals dictated by the environment."

Young defines [185] a real-time system as "any information processing activity or system which has to respond to externally generated input stimuli within a finite and specified period."

The Oxford Dictionary of Computing states [164] that "Any system in which the time at which output is produced is significant. This is usually because the input corresponds to some movement in the physical world, and the output has to relate to that same movement. The lag from input time to output time must be sufficiently small for acceptable timeliness."

Burns et al. emphasize [34] a pivotal aspect that distinguishes real-time systems from other systems: "the correctness of a real-time system depends not only on

the logical result of the computation, but also on the time at which the results are produced."

Real-time computation is said to be failed if it is not completed before its deadline, regardless of the amount of work that a computer system performed during the corresponding period of time. If the system in consideration tolerates no missed deadlines at all (e.g., possibly because of catastrophic consequences), then it is called hard real-time. Otherwise, the term soft real-time for the system is used. Where to put the borderline between hard real-time systems and soft real-time systems greatly depends on the applications domain, but for system development, being hard real-time means satisfying much stricter timeliness guarantees.

The purpose of real-time computing is to execute *tasks* in a timely manner. A task is an abstract entity of execution that can be substituted by those of "real-world" computer systems (e.g., a process, a thread, etc.). Each task has resource requirements. All tasks require some execution time on a processor and also a task may require a certain amount of memory, access to a bus, etc. Sometimes, a resource is only used by one task, but in other cases, resources are shared, which may require some control over the access to the resource. The same resource may be exclusively or non-exclusively accessed, depending on the operation to be performed on it, e.g., memory object (writing is exclusive but reading is non-exclusive).

The *release* time of a task is the time at which all the data, that are required to begin executing the task, are available and the *deadline* is the time by which the task must complete its execution. If a time-critical task does not successfully complete by its deadline, a *timing fault* occurs. In such situation the result of the task execution becomes of little or even no use.

In real-life systems, the goal of meeting all the deadlines is challenging because of dynamic factors (e.g., variations in processing times) that occur because of the system indeterminism imposed by sophisticated hardware and software components. One way to deal with these difficulties is presented in an approach that trades off result quality to meet execution requirements via *imprecise computation* [42]. The basic idea underneath the imprecise computation is to process first a mandatory workload and only then catch up with less important work. This principle of prioritizing important part of work at a price of leaving non-mandatory part to be potentially unfinished is implemented via augmenting traditional task model that was presented above. The system designer has to structure a time-critical task to contain a *mandatory subtask* and an *optional subtask*. To get an acceptable result of a task, its mandatory subtask has to be processed before the task's deadline. The further execution of the optional subtask is supposed to refine the intermediate result obtained by the mandatory subtask. If the optional subtask will complete successfully, the refined result is called *precise* and is assumed to have a zero-error. Otherwise, the *imprecise* intermediate result is promoted to be the final result of the task and is usually associated with some degree of error.

Thus, imprecise computation prevents timing faults by providing an approximate result of a reasonable quality whenever obtaining an exact result in time is not possible. This approach is suitable for applications featuring *monotonicity* – a property which requires that the quality of the intermediate result does not decrease with increasing processing time. This property is common for many algorithms in the areas of sorting, heuristic search, numerical computations, database query processing, etc.

In real-time systems domain, task is described by a piece of code that is executed in a repetitive manner. Every distinct execution of that code, say of some task  $\tau_i$ , corresponds to one more task instance called  $job\ J_{i,j}$  (a job j of a task  $\tau_i$ ) being released. In terms of repeatability, tasks may be categorized in three different families: periodic, sporadic or aperiodic.

According to the periodic task model [126] a task  $\tau_i$  is periodic if it is released periodically, let us say every  $T_i$  time units (the respective *period* of the task  $\tau_i$ ). The

periodicity constraint requires the task to run exactly once every period, but it does not require that the task be run exactly one period apart. Quite commonly, the period of a task is also its deadline. Task invocations usually are also called *job releases* or *job arrivals*. The worst-case execution requirements  $C_i$  is the maximum amount of time needed for execution of each job that was generated by  $\tau_i$ .

The task is sporadic if it is not periodic, but may be invoked at irregular intervals [146]. In this context,  $T_i$  denotes the respective minimum inter-arrival time. Sporadic tasks are characterized by an upper bound on the rate at which they may be invoked.

Aperiodic tasks are defined to be not periodic and have no upper bound on their invocation rate.

To measure how the collection of n tasks assigned to a single processor utilize this processor, the system  $utilization\ U$  is defined as:

$$U = \sum_{i=1}^{n} \frac{C_i}{T_i}$$

This definition of the uniprocessor utilization is made subject to an assumption that the processor is allowed to execute at most a single task at a time, and a task (as well as its jobs) cannot execute on two or more processors simultaneously. For the case of multiprocessor system that includes m identical processors, the definition of the computing system utilization can be extended as follows:

$$U = \frac{1}{m} \cdot \sum_{i=1}^{n} \frac{C_i}{T_i}$$

The scientific discipline of real-time systems considers two problems (i) schedulability analysis and (ii) Worst-Case Execution Time (WCET) analysis.

An objective of WCET analysis is to derive the values of the worst-case execution times  $C_i$  for every task  $\tau_i$  of a task set under consideration. Then, these values of  $C_i$

are submitted to the schedulability analysis as an input. The goal of the schedulability analysis is to find out whether the task set is *schedulable*.

A collection of tasks is schedulable by a scheduling algorithm SA if this algorithm ensures that the timing constraints of all tasks are met.

A task schedule is said to be *feasible* if all the tasks start after their release times and complete before their deadlines.

The utilization bound  $UB_{SA}$  of an algorithm SA is the maximum number such that if  $U \leq UB_{SA}$ , then all tasks meet their deadlines when scheduled by SA.

A schedule may be prepared before (offline scheduling), or obtained dynamically (online scheduling). Offline scheduling involves scheduling in advance of the operation, with specification of when the periodic tasks will be run and slots for sporadic or aperiodic tasks in the event that they are invoked. In online scheduling the tasks are scheduled as they arrive in the system. The corresponding algorithm should be as fast as is necessary to leave sufficient time for tasks to meet their deadlines.

The schedule of tasks may be preemptive or non-preemptive. A schedule is preemptive if tasks can be interrupted by other tasks and then resumed. This allows higher-priority tasks to preempt lower-priority tasks (whether these priorities are static or dynamic), in order to meet deadlines. Preemption allows the flexibility of not committing the processor to run a task through to completion once we start executing it. By contrast, once a task is begun in a non-preemptive schedule, it must be run to completion or until it gets blocked over a resource.

Examples of scheduling algorithms with a rich literature of associated schedulability analyses include Rate-Monotonic (RM), Earliest-Deadline-First (EDF) [126] for uniprocessor systems. On the other hand, the majority of scheduling problems on systems with more than two processors are NP-complete [43], thus for their solving some heuristics are usually utilized. A lot of them are based on uniprocessor scheduling. In such cases the problem of developing a multiprocessor schedule consists of

two subproblems. The first one is about assigning tasks to a processor. The second subproblem is about running uniprocessor scheduling algorithm for each processor and the corresponding task subset, in order to meet the respective deadlines. Often, in engineering practice multiple iterations of these two steps (in a loop) are performed until a feasible schedule is found.

The scheduling approach described above is termed *partitioned*. Its main strengths are the simplicity (stemming from the decomposition to multiple uniprocessor scheduling problems) and the ability to use the state-of-the-art uniprocessor scheduling algorithms known for their efficiency. The main weakness of partitioning is that the utilization bound of such approaches is inherently limited to 50% or less [159].

At the other end of the classification spectrum from partitioning, lies global scheduling [120], [51]. Algorithms of this category employ a single run-queue for all ready tasks. At any time instant, the highest-priority ready tasks execute, each on a different processor. This implies that task *migration* is allowed: each task may execute on any processor and in fact, it may migrate to another processor halfway through its execution.

Policies familiar from uniprocessor scheduling have been extended to global scheduling as well (global EDF, global RM) but their respective utilization bounds are much lower than even 50 % of their partitioned versions. Some other global scheduling algorithms (such as those from the proportionate fair (Pfair) [13] family) have a utilization bound of 100% [3], but are impractical from an implementation perspective because of the high number of preemptions.

Consequently, researchers have turned to semi-partitioned schemes, which try to combine the best of partitioned and migrative scheduling. Under such schemes (e.g., EDF-WM [100], EDDP [106], NPS-F [29]), only a few tasks migrate, in a very controlled manner. This allow efficient processor utilization (and utilization bounds above 50%) without the overheads of global scheduling.

The scheduling algorithms mentioned above were proposed in the context of the traditional task model described in this section. However, a principal factor that influences the success of one or another scheduling theory to a particular real-life application, is whether the underlying task model fits to the corresponding application domain. Naturally, the traditional task model, briefly described above, is not a "silver bullet". Hence, the real-time research community proposed other models, which we are going to discuss next.

#### 3.2 Rate-Based Execution model

Jeffay et al. presented [97] a generalization of the sporadic task model [146] and the periodic task model [126]. Unlike these two models that characterize a task under consideration using an exact value or a lower bound on the inter-arrival time of its jobs respectively, the authors considered an expected arrival rate of the jobs. In other words, the researchers do not make assumptions about the time instants at which the jobs arrive. Instead, they assume that the jobs arrive at a given average rate, while the corresponding distribution of the arrival time instances is arbitrary. Thus, they called this approach Rate-Based Execution (RBE) model. The motivation of RBE is supported by an observation that in many applications with timing constraints (e.g., digital signal processing or multimedia systems) the arrival of the events does not match well enough neither periodic nor sporadic task models. For instance, the video streaming applications are usually characterized by arbitrary instantaneous reception rates of video frames, while the respective average rates are kept pre-defined.

Therefore, the RBE task is defined through the following parameters:

- the length of the time interval that was chosen for the rate characterization;

- the maximum number of task instances (jobs) arrived per time interval specified above;

- the relative deadline of the task instance;

- the worst-case execution requirement of the task instance.

The authors observed that in the context of EDF-based scheduling, the feasibility of RBE task sets is a function of the distribution in time of the respective deadlines. Taking into account, that applications usually have some level of control over the deadlines (e.g., the deadline assignment is done by the operating system), the researchers argued that the real-time system designer is supposed to have more control over the operating systems rather than over the external processes that provide the system with the workload. Thus, the deadline-based scheduling is more appropriate to the RBE task sets when compared to priority-based scheduling where the feasibility of RBE task sets is a function of the rate at which the respective jobs arrive.

Focusing on the event-driven real-time systems, the applicability of the RBE model to the signal processing workloads was demonstrated [71] by Goddard et al. Earlier, Jeffay et al. have motivated [96] the use of the RBE model for the multimedia computing.

The above approaches consider non-parallel (i.e., sequential as in Section 3.1) tasks. Although the sequential task models simplify the complexitiy of the timing analysis and the scheduling, these models are restrictive for the most of the modern commercial-off-the-shelf hardware since they do not allow to exploit underlying parallelism properly. Thus, to take an advantage of the potential parallelism, the community was developing more adequate models of the tasks.

#### 3.3 Parallel task models

Parallel hardware architectures allow to decrease the execution time of the tasks and improve the utilization of the processors by splitting the tasks into smaller entities of computation (e.g., threads) that can be executed in parallel on different computa-

tional units (e.g., cores). Although, this led to shorter response times and improved schedulability, the problems of timing analysis and scheduling are getting one more dimension in terms of complexity. To handle this execution paradigm, the literature offers techniques and models for *parallel tasks*, implemented as multiple parallel threads. In this context, there are two common scenarios:

- the threads are organized in a "gang", where all the threads execute or become idle all together in parallel on different computational units (the *gang model*);

- the threads tend to perform execution independently and synchronize at the beginning and at the finishing of the execution (the *independent thread model*).

#### 3.3.1 Gang model